NB6N11S

NB6N11S is Input to LVDS Fanout Buffer/Translator manufactured by onsemi.

3.3 V 1:2 Any Level E Input to LVDS Fanout Buffer / Translator

Description The NB6N11S is a differential 1:2 Clock or Data Receiver and will accept Any Level input signals: LVPECL, CML, LVCMOS, LVTTL, or LVDS. These signals will be translated to LVDS and two identical copies of Clock or Data will be distributed, operating up to 2.0 GHz or 2.5 Gb/s, respectively. As such, the NB6N11S is ideal for SONET, Gig E, Fiber Channel, Backplane and other Clock or Data distribution applications.

The NB6N11S has a wide input mon mode range from GND + 50 m V to VCC

- 50 m V. bined with the 50 W internal termination resistors at the inputs, the NB6N11S is ideal for translating a variety of differential or single- ended Clock or Data signals to 350 m V typical LVDS output levels.

The NB6N11S is functionally equivalent to the EP11, LVEP11, SG11 or 7L11M devices and is offered in a small, 3 mm X 3 mm, 16- QFN package. Application notes, models, and support documentation are available at .onsemi..

The NB6N11S is a member of the ECLin PS MAX™ family of high performance products.

Features

- Maximum Input Clock Frequency > 2.0 GHz

- Maximum Input Data Rate > 2.5 Gb/s

- 1 ps Maximum of RMS Clock Jitter

- Typically 10 ps of Data Dependent Jitter

- 380 ps Typical Propagation Delay

- 120 ps Typical Rise and Fall Times

- Functionally patible with Existing 3.3 V LVEL, LVEP, EP, and

SG Devices

- These are Pb- Free Devices

.onsemi.

QFN- 16 MN SUFFIX CASE 485G

MARKING DIAGRAM-

16 1

NB6N 11S ALYW G

A = Assembly Location L = Wafer Lot Y = Year W = Work Week G = Pb- Free Package

(Note: Microdot may be in either location)

- For additional marking information, refer to Application Note AND8002/D.

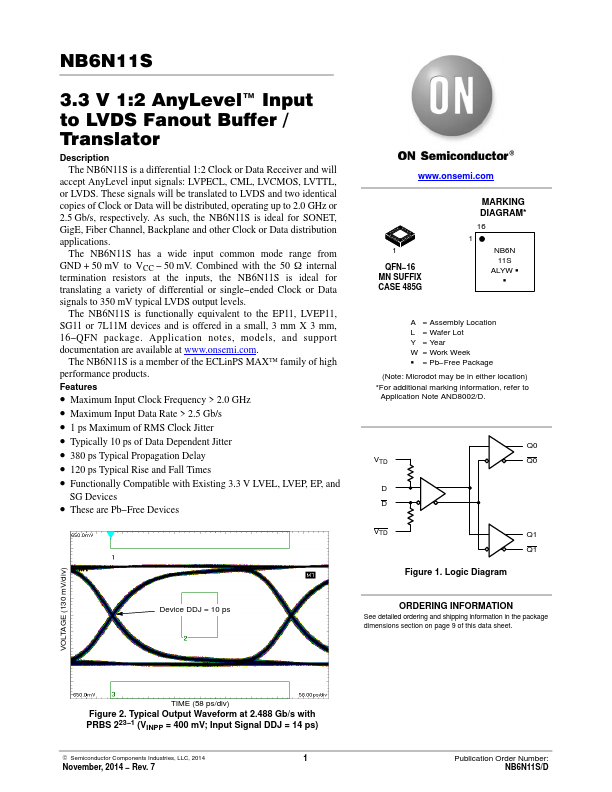

Q0

Q0

Q1

Q1

Figure 1. Logic Diagram

Device DDJ = 10...