NB7L111M Description

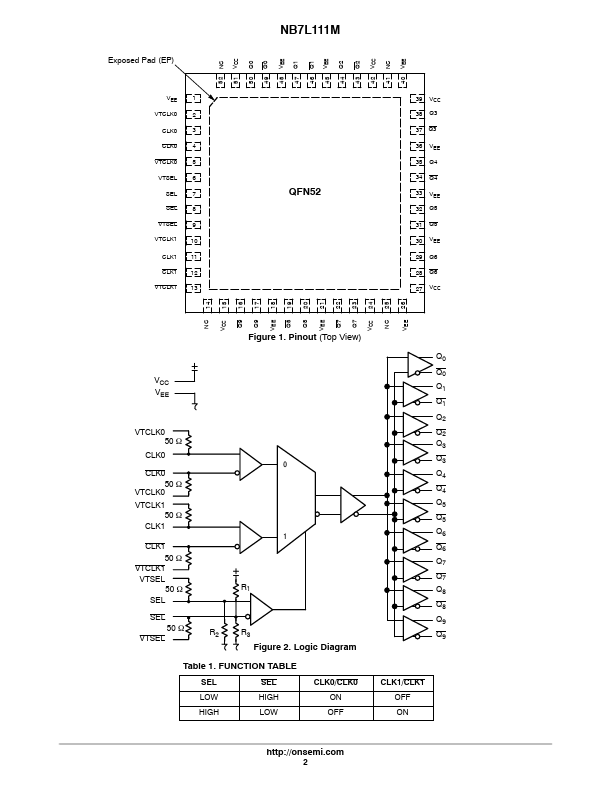

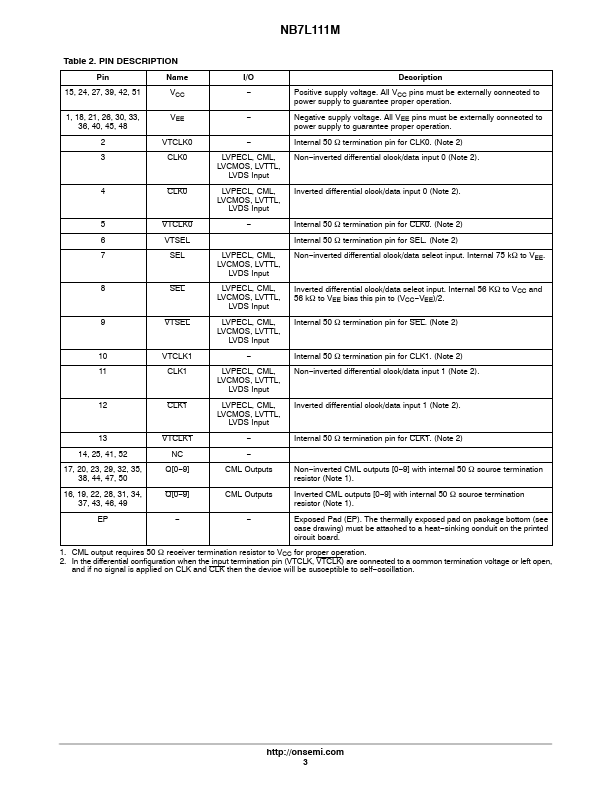

The NB7L111M is a low skew 1 to 10 differential clock/data driver, designed with clock/data distribution in mind. It accepts two clock/data sources into multiplexer input and reproduces ten identical CML differential outputs. This device is ideal for clock/data distribution across the backplane or a board, and redundant clock switchover applications.

NB7L111M Key Features

- For additional marking information, refer to Application Note AND8002/D

- For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering

- Rev. 1