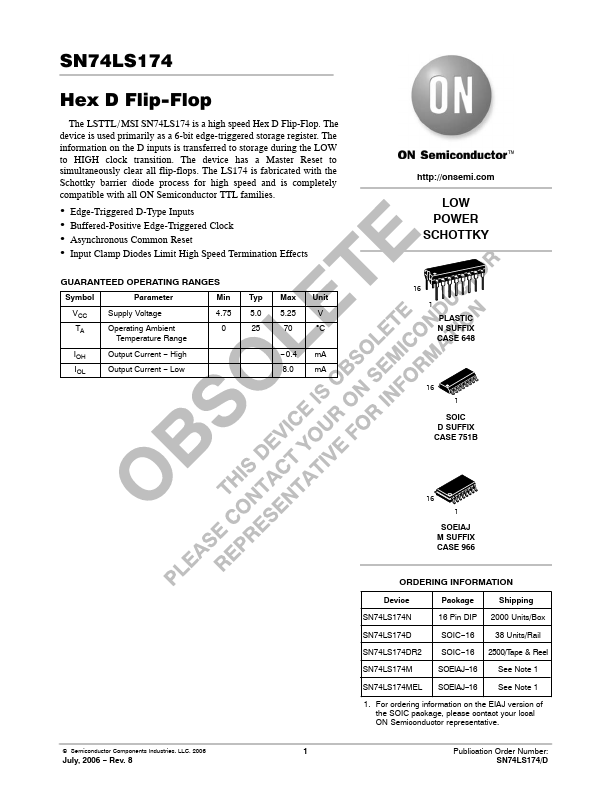

| Part | SN74LS174 |

|---|---|

| Description | Hex D Flip-Flop |

| Manufacturer | onsemi |

| Size | 178.06 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SN74LS174 | Motorola Semiconductor | HEX D FLIP-FLOP |

| SN74LS174 | Texas Instruments | HEX/QUADRUPLE D-TYPE FLIP-FLOPS |

| SN74LS174N | Texas Instruments | HEX/QUADRUPLE D-TYPE FLIP-FLOPS |

| SN74LS170 | Motorola Semiconductor | 4 x 4 REGISTER FILE OPEN-COLLECTOR |

| SN74LS173A | Motorola Semiconductor | 4-BIT D-TYPE REGISTER |