PI6C2405A

Overview

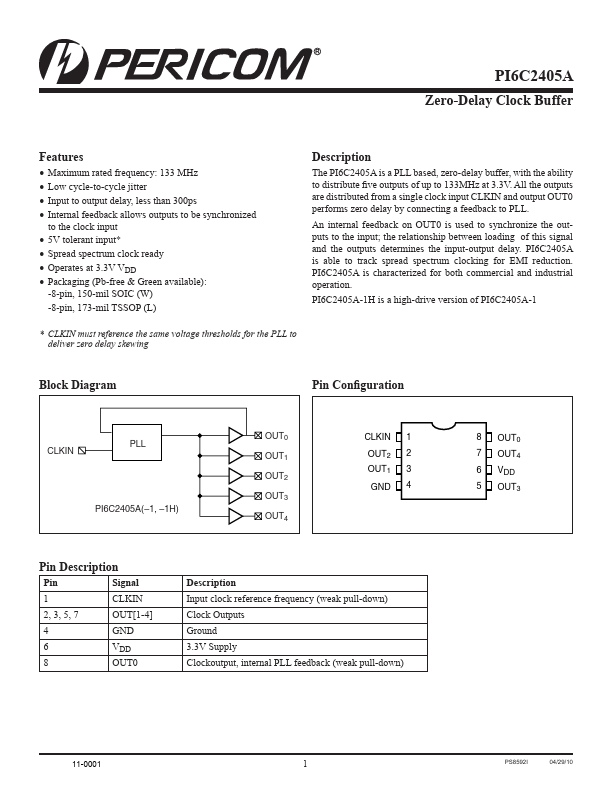

The PI6C2405A is a PLL based, zero-delay buffer, with the ability to distribute five outputs of up to 133MHz at 3.3V. All the outputs are distributed from a single clock input CLKIN and output OUT0 performs zero delay by connecting a feedback to PLL.

- Maximum rated frequency: 133 MHz Low cycle-to-cycle jitter Input to output delay, less than 300ps Internal feedback allows outputs to be synchronized to the clock input 5V tolerant input* Spread spectrum clock ready Operates at 3.3V VDD Packaging (Pb-free & Green available): -8-pin, 150-mil SOIC (W) -8-pin, 173-mil TSSOP (L)