PI6C2409

Overview

- Maximum rated frequency: 133 MHz Low cycle-to-cycle jitter Input to output delay, less than 200ps Internal feedback allows outputs to be synchronized to the clock input

- Operates at 3.3V VDD

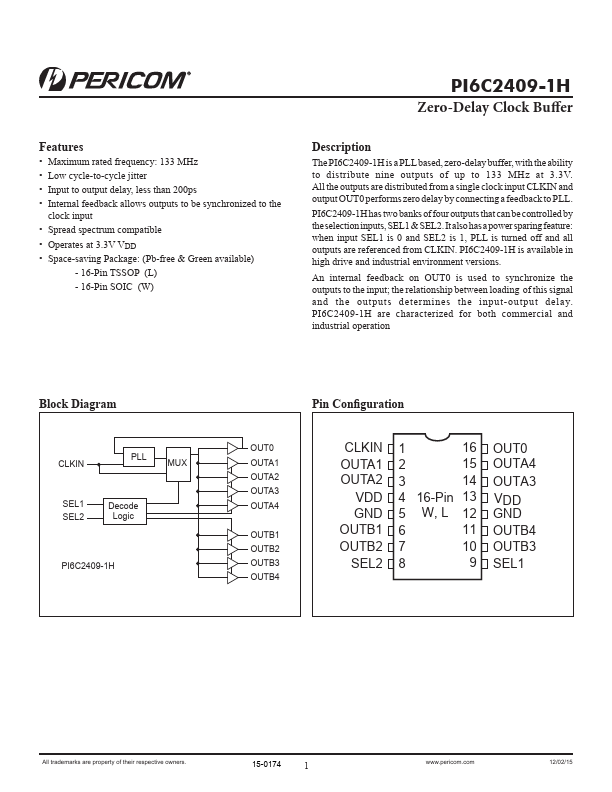

- Space-saving Packages: 150-mil SOIC (W) 173-mil TSSOP (L) Functional Description The PI6C2409 is a PLL based, zero-delay buffer, with the ability to distribute nine outputs of up to 133MHz at 3.3V. All the outputs are distributed from a single clock input CLKIN and output OUT0 performs zero delay by connecting a feedback to PLL. PI6C2409 has two banks of four outputs that can be controlled by the selection inputs, SEL1 & SEL2. It also has a powersparing feature: when input SEL1 is 0 and SEL2 is 1, PLL is turned off and all outputs are referenced from CLKIN. PI6C2409 is available in high drive and industrial environment versions. An internal feedback on OUT0 is used to synchronize the outputs to the input; the relationship between loading of this signal and the outputs determines the input-output delay. PI6C2409 are characterized for both commercial and industrial operation