PI6CV857L Overview

Key Specifications

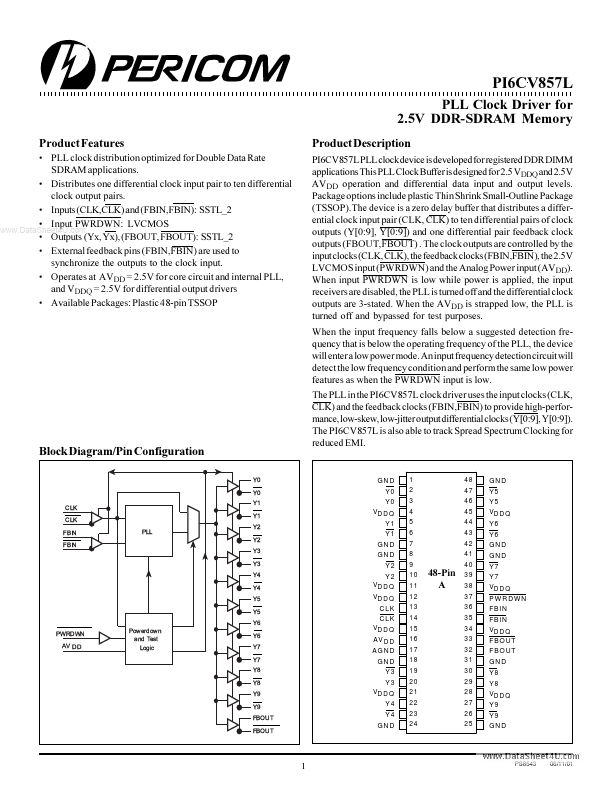

Package: TSSOP

Pins: 48

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Key Features

- PLL clock distribution optimized for Double Data Rate SDRAM applications

- Distributes one differential clock input pair to ten differential clock output pairs