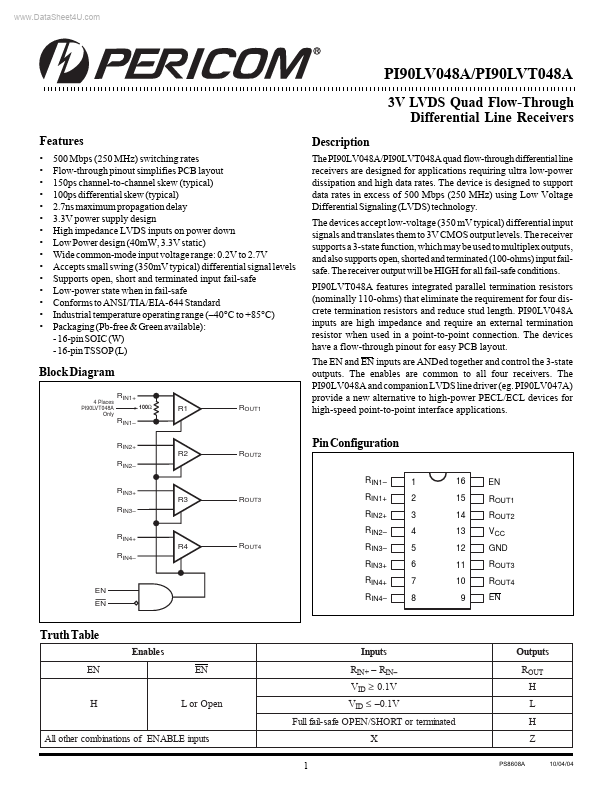

PI90LVB048A

PI90LVB048A is LVDS Quad Flow-Through Differential Line Receivers manufactured by Pericom Semiconductor.

- Part of the PI90LV048A comparator family.

- Part of the PI90LV048A comparator family.

Features

- -

- -

- -

- -

- -

- -

- -

- 500 Mbps (250 MHz) switching rates Flow-through pinout simplifies PCB layout 150ps channel-to-channel skew (typical) 100ps differential skew (typical) 2.7ns maximum propagation delay 3.3V power supply design High impedance LVDS inputs on power down Low Power design (40m W, 3.3V static) Wide mon-mode input voltage range: 0.2V to 2.7V Accepts small swing (350m V typical) differential signal levels Supports open, short and terminated input fail-safe Low-power state when in fail-safe Conforms to ANSI/TIA/EIA-644 Standard Industrial temperature operating range (- 40°C to +85°C) Packaging (Pb-free & Green available):

- 16-pin SOIC (W)

- 16-pin TSSOP (L)

Description

The PI90LV048A/PI90LVT048A quad flow-through differential line receivers are designed for applications requiring ultra low-power dissipation and high data rates. The device is designed to support data rates in excess of 500 Mbps (250 MHz) using Low Voltage Differential Signaling (LVDS) technology. The devices accept low-voltage (350 m V typical) differential input signals and translates them to 3V CMOS output levels. The receiver supports a 3-state function, which may be used to multiplex outputs, and also supports open, shorted and terminated (100-ohms) input failsafe. The receiver output will be HIGH for all fail-safe conditions. PI90LVT048A features integrated parallel termination resistors (nominally 110-ohms) that eliminate the requirement for four discrete termination resistors and reduce stud length. PI90LV048A inputs are high impedance and require an external termination resistor when used in a point-to-point connection. The devices have a flow-through pinout for easy PCB layout. The EN and EN inputs are ANDed together and control the 3-state outputs. The enables are mon to all four receivers. The PI90LV048A and panion LVDS line driver (eg. PI90LV047A) provide a new alternative to high-power PECL/ECL devices for high-speed point-to-point interface applications.

Block...