PLL520-88

PLL520-88 is (PLL520-8x) Low Phase Noise VCXO manufactured by PhaseLink Corporation.

Preliminary

..

PLL520-88/-89

Low Phase Noise VCXO (9.5-65MHz)

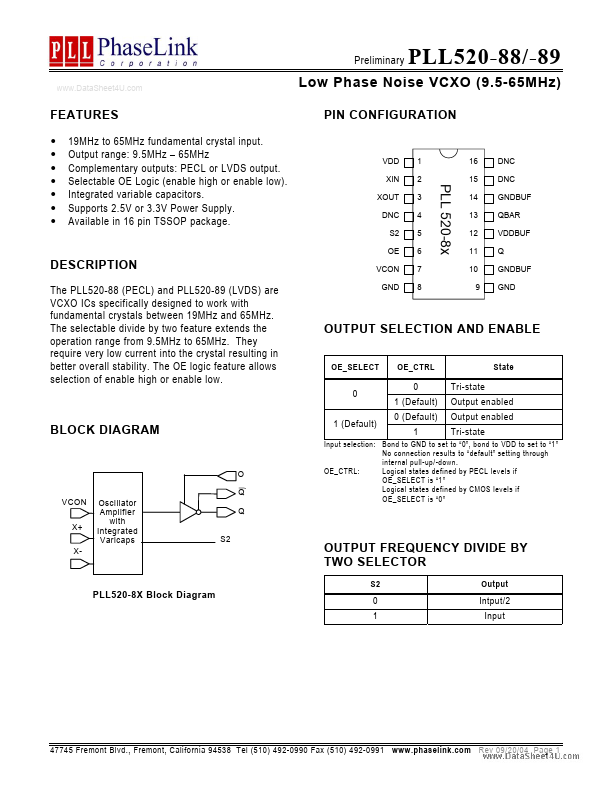

PIN CONFIGURATION

Features

- -

- -

- -

- 19MHz to 65MHz fundamental crystal input. Output range: 9.5MHz

- 65MHz plementary outputs: PECL or LVDS output. Selectable OE Logic (enable high or enable low). Integrated variable capacitors. Supports 2.5V or 3.3V Power Supply. Available in 16 pin TSSOP package.

VDD XIN XOUT DNC S2 OE

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

DNC DNC GNDBUF QBAR VDDBUF Q GNDBUF GND

PLL 520-8x

DESCRIPTION

The PLL520-88 (PECL) and PLL520-89 (LVDS) are VCXO ICs specifically designed to work with fundamental crystals between 19MHz and 65MHz. The selectable divide by two feature extends the operation range from 9.5MHz to 65MHz. They require very low current into the crystal resulting in better overall stability. The OE logic feature allows selection of enable high or enable low.

VCON GND

OUTPUT SELECTION AND ENABLE

OE_SELECT OE_CTRL State

BLOCK DIAGRAM

1 (Default)

0 1 (Default) 0 (Default) 1

Tri-state Output enabled Output enabled Tri-state

O Q VCON X+ XOscillator Amplifier with Integrated Varicaps Q S2

Input selection: Bond to GND to set to “0”, bond to VDD to set to “1” No connection results to “default” setting through internal pull-up/-down. OE_CTRL: Logical states defined by PECL levels if OE_SELECT is “1” Logical states defined by CMOS levels if OE_SELECT is “0”

OUTPUT FREQUENCY DIVIDE BY TWO SELECTOR

S2 Output

PLL520-8X Block...