QL16X24B

QL16X24B is Very-High-Speed CMOS FPGA manufactured by QuickLogic.

..

QL16x24B p ASIC® 1 Family Very-High-Speed CMOS FPGA

Rev C p ASIC HIGHLIGHTS Very High Speed

- Via Link® metal-to-metal programmable- via antifuse technology, allows counter speeds over 150 MHz and logic cell delays of under 2 ns. High Usable Density

- A 16-by-24 array of 384 logic cells provides 4,000 usable ASIC gates (7,000 PLD gates) in 84-pin PLCC, 100-pin and 144-pin TQFP, 144-pin CPGA and 160-pin CQFP packages. Low-Power, High-Output Drive

- Standby current typically 2 m A. A 16-bit counter operating at 100 MHz consumes less than 50 m A. Minimum IOL of 12 m A and IOH of 8 m A Low-Cost, Easy-to-Use Design Tools

- Designs entered and simulated using Quick Logic's new Quick Works® development environment, or with third-party CAE tools including Viewlogic, Synopsys, Mentor, Cadence and Veribest. Fast, fully automatic place and route on PC and workstation platforms using Quick Logic software.

…4,000 usable ASIC gates, 122 I/O pins

4 p ASIC 1

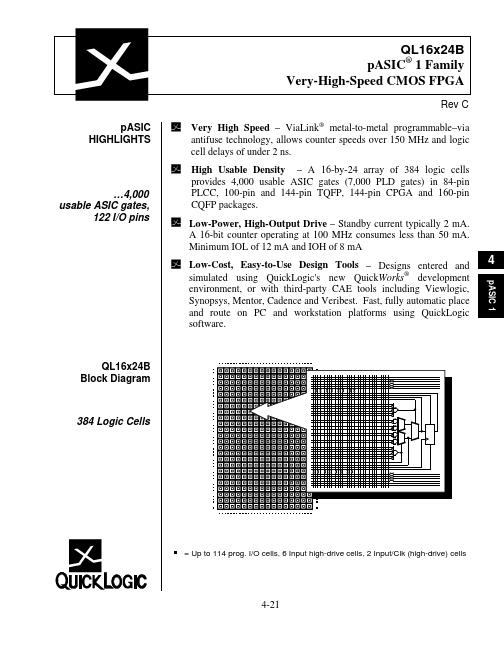

QL16x24B Block Diagram

384 Logic Cells

= Up to 114 prog. I/O cells, 6 Input high-drive cells, 2 Input/Clk (high-drive) cells

4-21

PRODUCT SUMMARY The QL16x24B is a member of the p ASIC 1 Family of very-high-speed CMOS user-programmable ASIC devices. The 384 logic cell fieldprogrammable gate array (FPGA) offers 4,000 usable ASIC gates (equivalent to 7,000 PLD gates) of high-performance general-purpose logic in 84-pin PLCC, 100-pin and 144-pin TQFP, 144-pin CPGA, and 160-pin CQFP. Low-impedance, metal-to-metal, Via Link interconnect technology provides nonvolatile custom logic capable of operating above 150 MHz. Logic cell delays under 2 ns, bined with input delays of under 1.5 ns and output delays under 3 ns, permit high-density programmable devices to be used with today’s fastest microprocessors and DSPs. Designs can be entered using Quick Logic’s Quick Works Toolkit or most populart third-party CAE tools. Quick Works bines Verilog/VHDL design entry and simulation tools with device-specific place &...