ICS671-03 Overview

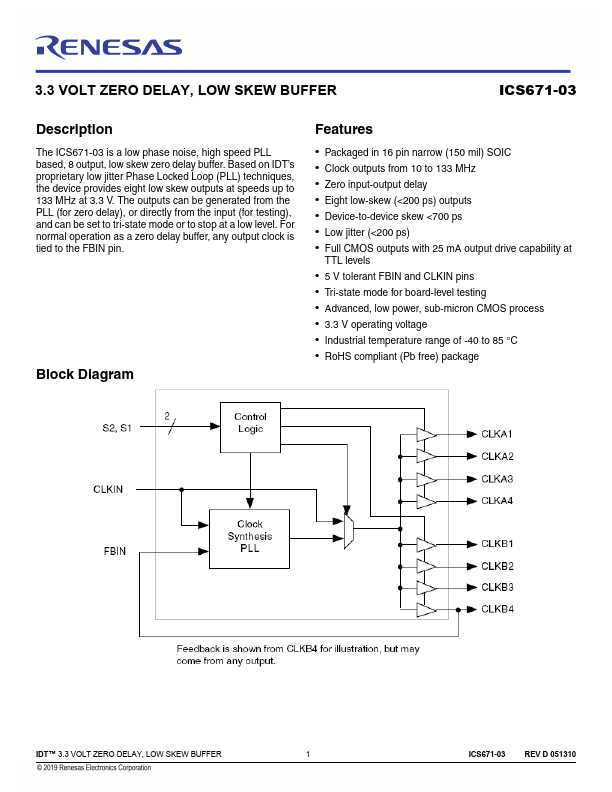

The ICS671-03 is a low phase noise, high speed PLL based, 8 output, low skew zero delay buffer. Based on IDT’s proprietary low jitter Phase Locked Loop (PLL) techniques, the device provides eight low skew outputs at speeds up to 133 MHz at 3.3 V. The outputs can be generated from the PLL (for zero delay), or directly from the input (for testing), and can be set to tri-state mode or to stop at a low level.

ICS671-03 Key Features

- Packaged in 16 pin narrow (150 mil) SOIC

- Clock outputs from 10 to 133 MHz

- Zero input-output delay

- Eight low-skew (<200 ps) outputs

- Device-to-device skew <700 ps

- Low jitter (<200 ps)

- Full CMOS outputs with 25 mA output drive capability at

- 5 V tolerant FBIN and CLKIN pins

- Tri-state mode for board-level testing

- Advanced, low power, sub-micron CMOS process