ICS91305

ICS91305 is High Performance Communication Buffer manufactured by Renesas.

High Performance munication Buffer

General Description

The ICS91305 is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the REF input with the CLKOUT signal. It is designed to distribute high speed clocks in munication systems operating at speeds from 10 to 133 MHz.

ICS91305 is a zero delay buffer that provides synchronization between the input and output. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than +/- 350 p S, the part acts as a zero delay buffer.

Features

- Zero input

- output delay

- Frequency range 10

- 133 MHz (3.3V)

- 5V tolerant input REF

- High loop filter bandwidth ideal for Spread

Spectrum applications.

- Less than 200 ps Jitter between outputs

- Skew controlled outputs

- Skew less than 250 ps between outputs

- Available in 8 pin 150 mil SOIC & 173 mil

TSSOP packages

- 3.3V ±10% operation

The ICS91305 es in an eight pin 150 mil SOIC package. It has five output clocks. In the absence of REF input, will be in the power down mode. In this mode, the PLL is turned off and the output buffers are pulled low. Power down mode provides the lowest power consumption for a standby condition.

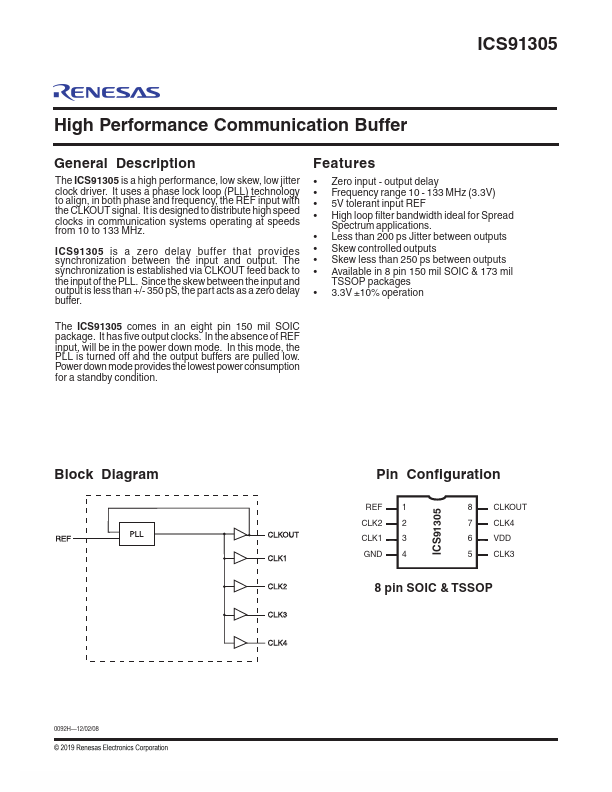

Block Diagram

Pin Configuration

REF 1 CLK2 2 CLK1 3 GND 4

8 CLKOUT 7 CLK4 6 VDD 5 CLK3

8 pin SOIC & TSSOP

0092H- 12/02/08

Pin Descriptions

PIN NUMBER 1 2 3 4 5 6 7 8

PIN NAME REF2 CLK23 CLK13 GND CLK33 VDD CLK43

CLKOUT3

TYPE...