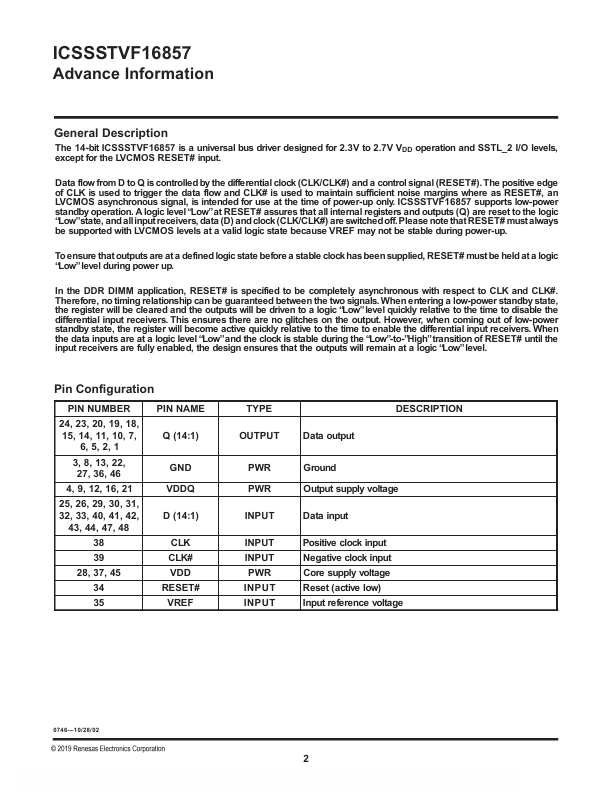

ICSSSTVF16857 Overview

�ENESAS ICSSSTVF16857 Advance Information DDR 14-Bit Registered Buffer Remended Applications: DDR Memory Modules Provides plete DDR DIMM logic solution with ICS93V857 or ICS95V857 SSTL_2 patible data registers Product.

ICSSSTVF16857 Key Features

- Differential clock signal

- Meets SSTL_2 signal data

- Supports SSTL_2 class I & II specifications

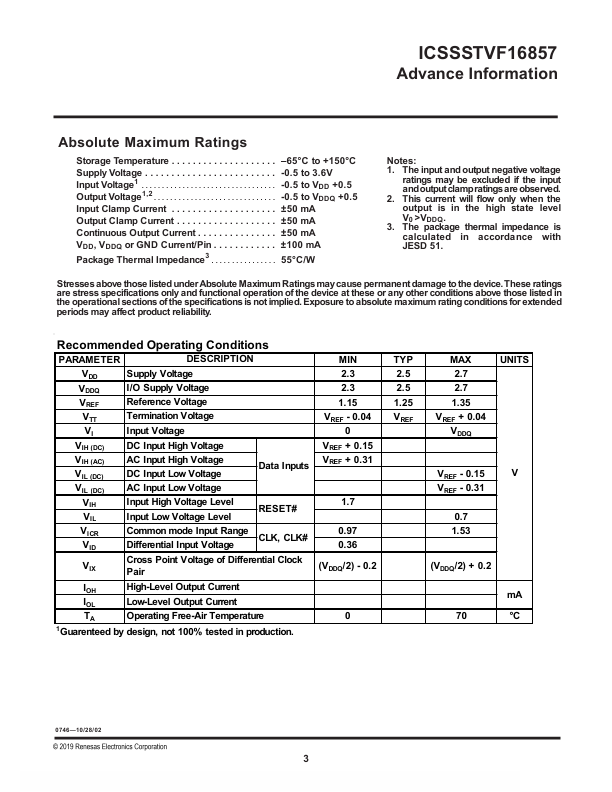

- Low-voltage operation

- Voo = 2.3V to2.7V

- 48 pin TSS OP and TVS OP package