IDT71V35761SA Overview

Key Specifications

Package: BGA

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Min Voltage (typical range): 3.135 V

Description

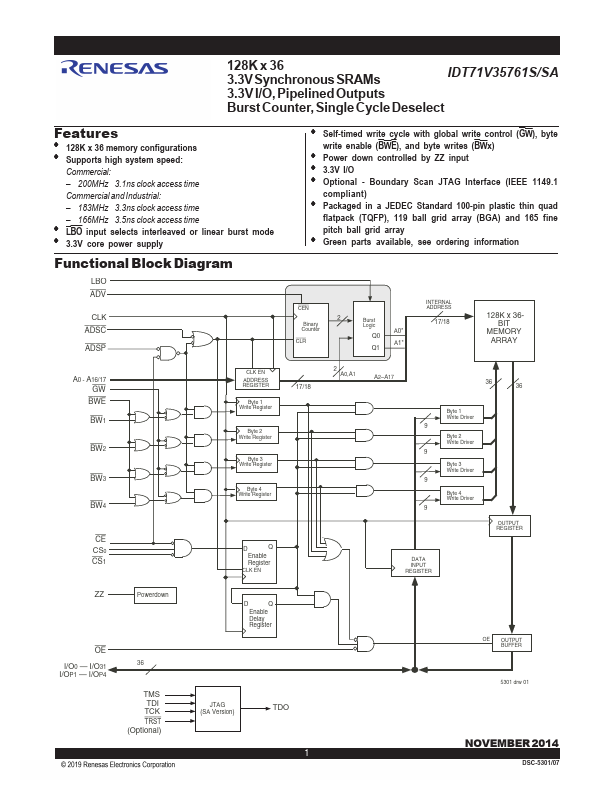

The IDT71V35761 are high-speed SRAMs organized as 128K x 36. The IDT71V35761 SRAMs contain write, data, address and controlregisters.

Key Features

- 128K x 36 memory configurations

- LBO input selects interleaved or linear burst mode

- 3.3V core power supply