MK2049-34

Overview

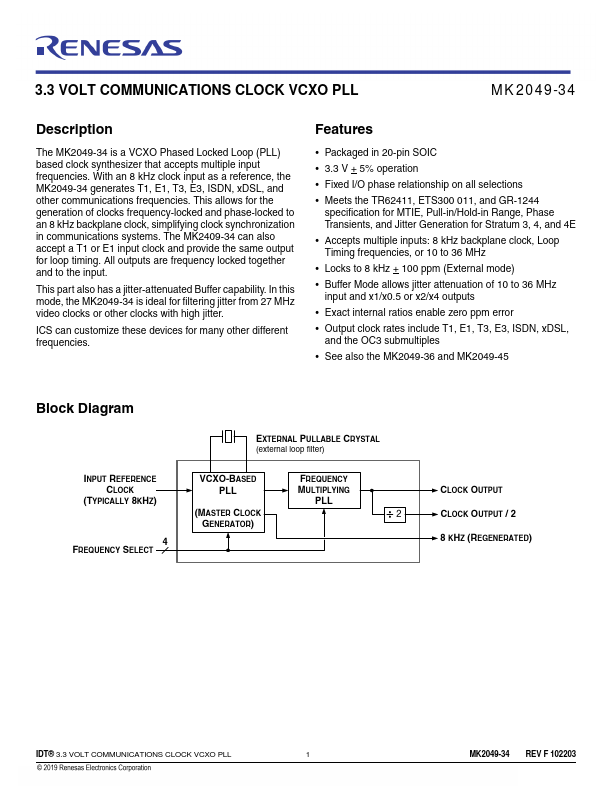

The MK2049-34 is a VCXO Phased Locked Loop (PLL) based clock synthesizer that accepts multiple input frequencies. With an 8 kHz clock input as a reference, the MK2049-34 generates T1, E1, T3, E3, ISDN, xDSL, and other communications frequencies.

- Packaged in 20-pin SOIC

- 3.3 V + 5% operation

- Fixed I/O phase relationship on all selections

- Meets the TR62411, ETS300 011, and GR-1244