MK2049-45 Overview

Description

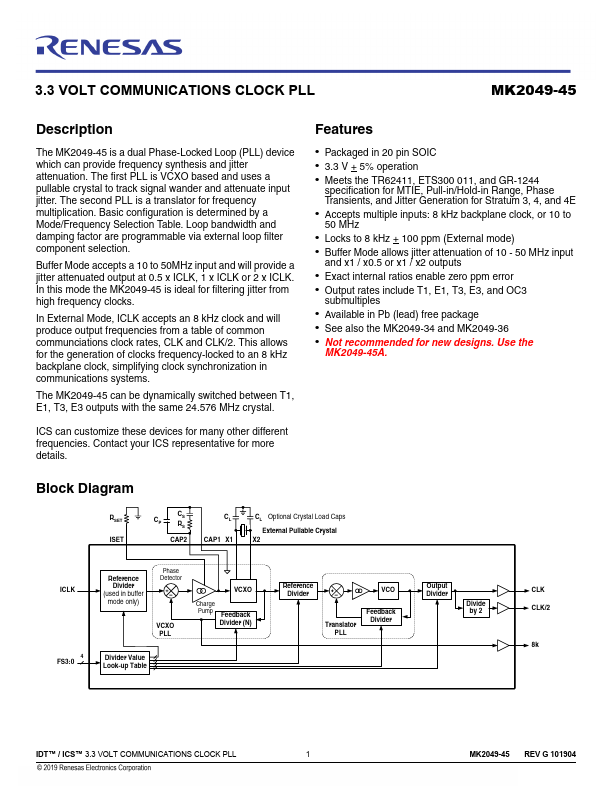

The MK2049-45 is a dual Phase-Locked Loop (PLL) device which can provide frequency synthesis and jitter attenuation. The first PLL is VCXO based and uses a pullable crystal to track signal wander and attenuate input jitter.

Key Features

- Packaged in 20 pin SOIC

- 3.3 V + 5% operation

- Accepts multiple inputs: 8 kHz backplane clock, or 10 to 50 MHz

- Locks to 8 kHz + 100 ppm (External mode)

- Buffer Mode allows jitter attenuation of 10 - 50 MHz input and x1 / x0.5 or x1 / x2 outputs

- Exact internal ratios enable zero ppm error

- Output rates include T1, E1, T3, E3, and OC3 submultiples

- Available in Pb (lead) free package

- Not recommended for new designs. Use the MK2049-45A