R5F513T3AGFL

R5F513T3AGFL is 32-MHz 32-bit RX MCU manufactured by Renesas.

- Part of the R5F513T5ADFL comparator family.

- Part of the R5F513T5ADFL comparator family.

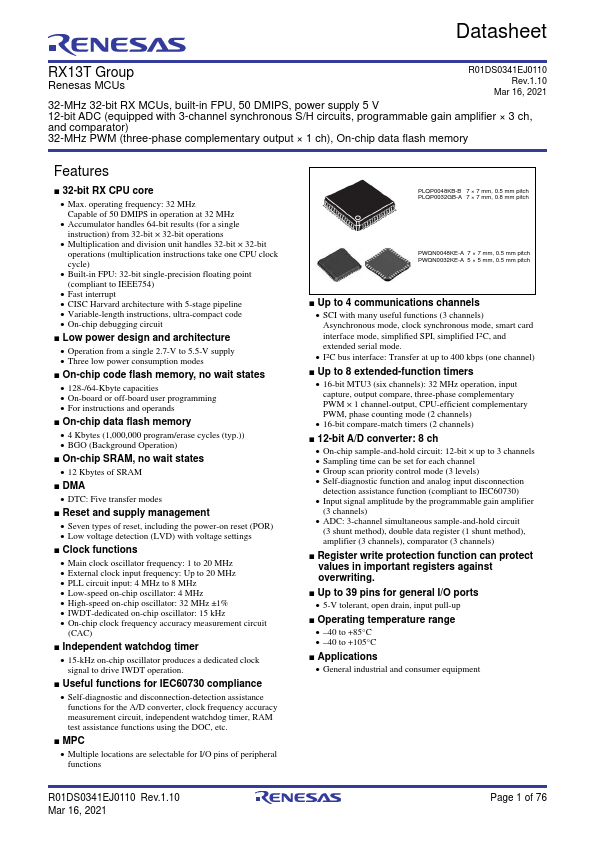

RX13T Group

Renesas MCUs

R01DS0341EJ0110 Rev.1.10

Mar 16, 2021

32-MHz 32-bit RX MCUs, built-in FPU, 50 DMIPS, power supply 5 V 12-bit ADC (equipped with 3-channel synchronous S/H circuits, programmable gain amplifier × 3 ch, and parator) 32-MHz PWM (three-phase plementary output × 1 ch), On-chip data flash memory

Features

- 32-bit RX CPU core

- Max. operating frequency: 32 MHz Capable of 50 DMIPS in operation at 32 MHz

- Accumulator handles 64-bit results (for a single instruction) from 32-bit × 32-bit operations

- Multiplication and division unit handles 32-bit × 32-bit operations (multiplication instructions take one CPU clock cycle)

- Built-in FPU: 32-bit single-precision floating point (pliant to IEEE754)

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length instructions, ultra-pact code

- On-chip debugging circuit

- Low power design and architecture

- Operation from a single 2.7-V to 5.5-V supply

- Three low power consumption modes

- On-chip code flash memory, no wait states

- 128-/64-Kbyte capacities

- On-board or off-board user programming

- For instructions and operands

- On-chip data flash memory

- 4 Kbytes (1,000,000 program/erase cycles (typ.))

- BGO (Background Operation)

- On-chip SRAM, no wait states

- 12 Kbytes of SRAM

- DMA

- DTC: Five transfer modes

- Reset and supply...