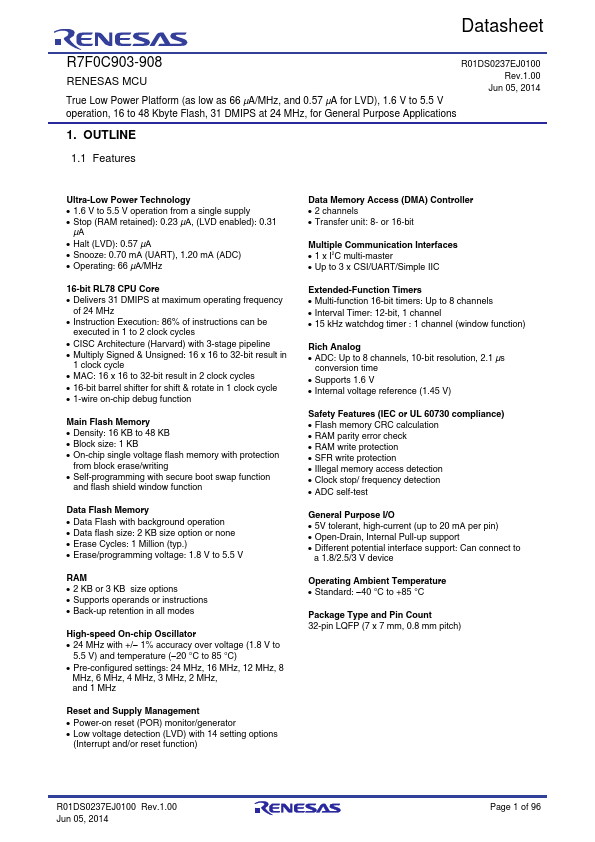

R7F0C907

R7F0C907 is MCU manufactured by Renesas.

- Part of the R7F0C903 comparator family.

- Part of the R7F0C903 comparator family.

Features

Ultra-Low Power Technology

- 1.6 V to 5.5 V operation from a single supply

- Stop (RAM retained): 0.23 µA, (LVD enabled): 0.31

µA

- Halt (LVD): 0.57 µA

- Snooze: 0.70 m A (UART), 1.20 m A (ADC)

- Operating: 66 µA/MHz

16-bit RL78 CPU Core

- Delivers 31 DMIPS at maximum operating frequency of 24 MHz

- Instruction Execution: 86% of instructions can be executed in 1 to 2 clock cycles

- CISC Architecture (Harvard) with 3-stage pipeline

- Multiply Signed & Unsigned: 16 x 16 to 32-bit result in

1 clock cycle

- MAC: 16 x 16 to 32-bit result in 2 clock cycles

- 16-bit barrel shifter for shift & rotate in 1 clock cycle

- 1-wire on-chip debug function

Main Flash Memory

- Density: 16 KB to 48 KB

- Block size: 1 KB

- On-chip single voltage flash memory with protection from block erase/writing

- Self-programming with secure boot swap function and flash shield window function

Data Flash Memory

- Data Flash with background operation

- Data flash size: 2 KB size option or none

- Erase Cycles: 1 Million (typ.)

- Erase/programming voltage: 1.8 V to 5.5 V

- 2 KB or 3 KB size options

- Supports operands or instructions

- Back-up retention in all modes

High-speed On-chip Oscillator

- 24 MHz with +/- 1% accuracy over voltage (1.8 V to

5.5 V) and temperature (- 20 °C to 85 °C)

- Pre-configured settings: 24 MHz, 16 MHz, 12 MHz, 8

MHz, 6 MHz, 4 MHz, 3 MHz, 2 MHz, and 1 MHz

Reset and Supply Management

- Power-on reset (POR) monitor/generator

- Low voltage detection (LVD) with 14 setting options

(Interrupt and/or reset...