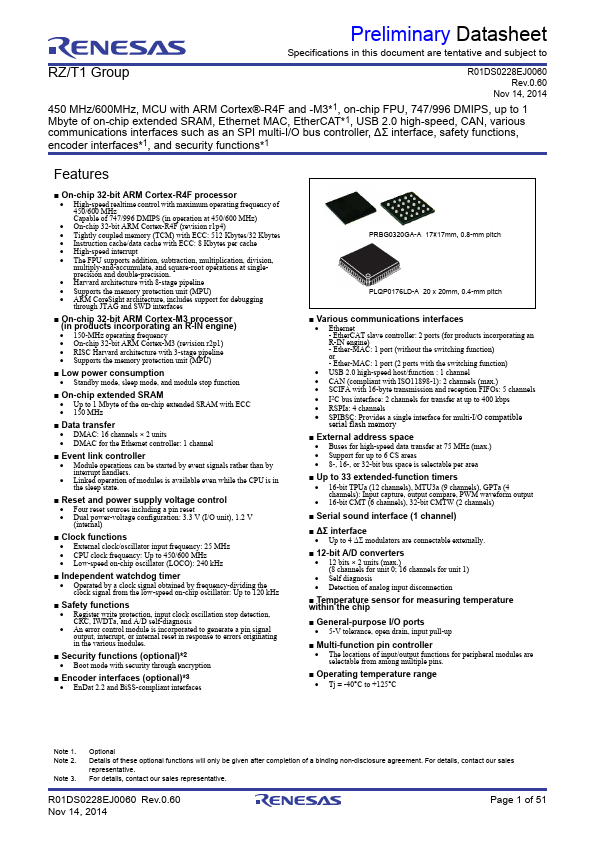

R7S910017CBG

R7S910017CBG is 450MHz / 600MHz MCU manufactured by Renesas.

- Part of the R01-DS0228 comparator family.

- Part of the R01-DS0228 comparator family.

Features

- On-chip 32-bit ARM Cortex-R4F processor

- High-speed realtime control with maximum operating frequency of 450/600 MHz Capable of 747/996 DMIPS (in operation at 450/600 MHz)

- On-chip 32-bit ARM Cortex-R4F (revision r1p4)

- Tightly coupled memory (TCM) with ECC: 512 Kbytes/32 Kbytes

- Instruction cache/data cache with ECC: 8 Kbytes per cache

- High-speed interrupt

- The FPU supports addition, subtraction, multiplication, division, multiply-and-accumulate, and square-root operations at singleprecision and double-precision.

- Harvard architecture with 8-stage pipeline

- Supports the memory protection unit (MPU)

- ARM Core Sight architecture, includes support for debugging through JTAG and SWD interfaces

- (Oinn-pcrhoidpu3c2ts-biint c Ao Rrp Mo Craotrintegxa-Mn3Rp-Ir Noceensgsinoer )

- 150-MHz operating frequency

- On-chip 32-bit ARM Cortex-M3 (revision r2p1)

- RISC Harvard architecture with 3-stage pipeline

- Supports the memory protection unit (MPU)

- Low power consumption

- Standby mode, sleep mode, and module stop function

- On-chip extended SRAM

- Up to 1 Mbyte of the on-chip extended SRAM with ECC

- 150 MHz

- Data transfer

- DMAC: 16 channels × 2 units

- DMAC for the Ethernet controller: 1 channel

- Event link controller

- Module operations can be started by event signals rather than by interrupt handlers.

- Linked operation of modules is available even while the CPU is in the sleep state.

- Reset and power supply voltage control

- Four reset sources including a pin reset

- Dual power-voltage configuration: 3.3 V (I/O unit), 1.2 V (internal)

- Clock functions

- External clock/oscillator input frequency: 25 MHz

- CPU clock frequency: Up to 450/600 MHz

- Low-speed on-chip oscillator (LOCO): 240 k Hz

- Independent watchdog timer

- Operated by a clock signal obtained by frequency-dividing the clock signal from the low-speed on-chip oscillator: Up to 120 k Hz

- Safety functions

- Register write protection, input clock oscillation stop detection, CRC, IWDTa, and A/D...