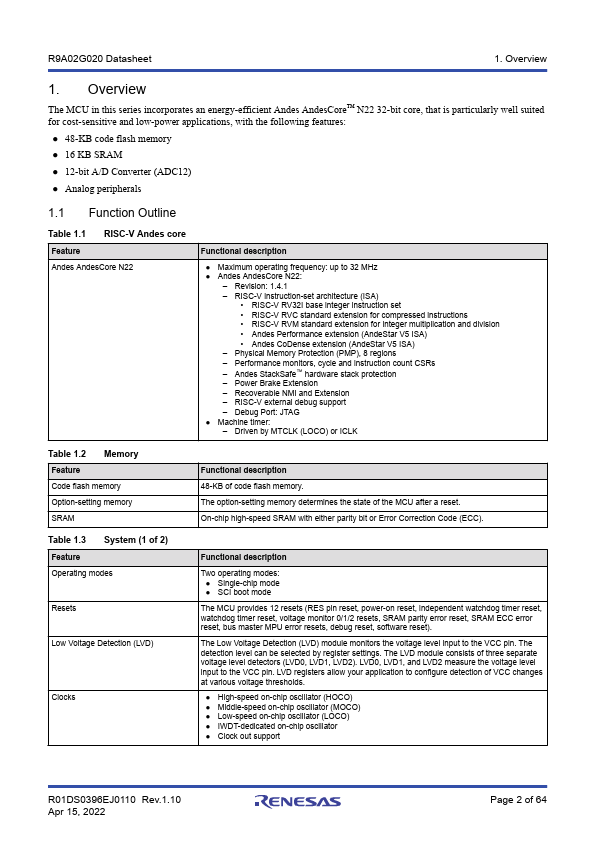

R9A02G020 Description

Maximum operating frequency: up to 32 MHz Andes AndesCore N22: 1.4.1 RISC-V instruction-set architecture (ISA) RISC-V RV32I base integer instruction set RISC-V RVC standard extension for pressed instructions RISC-V RVM standard extension for integer multiplication and division Andes Performance extension (AndeStar V5 ISA) Andes CoDense extension (AndeStar V5 ISA) Physical Memory.

R9A02G020 Key Features

- RISC-V Andes N22 Core

- RISC-V instruction-set architecture (RV32I)

- Maximum operating frequency: 32 MHz

- Andes Physical Memory Protection unit (Andes PMP)

- Debug and Trace: RISC-V External Debug Support

- Debug Port: JTAG

- Memory

- 48-KB code flash memory

- 16 KB SRAM

- Memory protection units