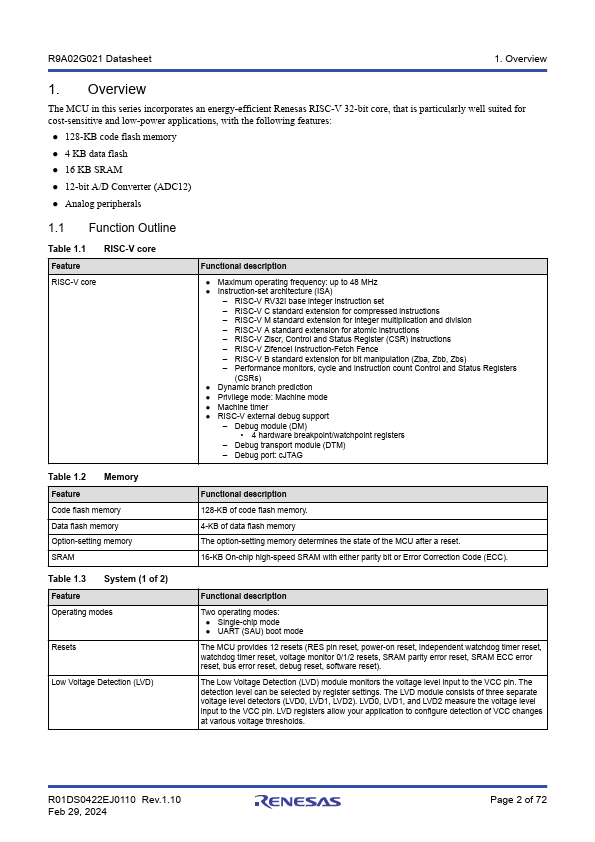

R9A02G021 Key Features

- RISC-V Core

- Renesas RISC-V instruction-set architecture (RV32I [MACB])

- Maximum operating frequency: 48 MHz

- Debug and Trace: RISC-V External Debug Support

- Debug Port: cJTAG

- 32-pin HWQFN (5 mm × 5 mm, 0.5 mm pitch)

- 24-pin HWQFN (4 mm × 4 mm, 0.5 mm pitch)

- 16-pin WLCSP(1.99 mm × 1.99 mm, 0.4 mm pitch)

- Memory

- 128-KB code flash memory