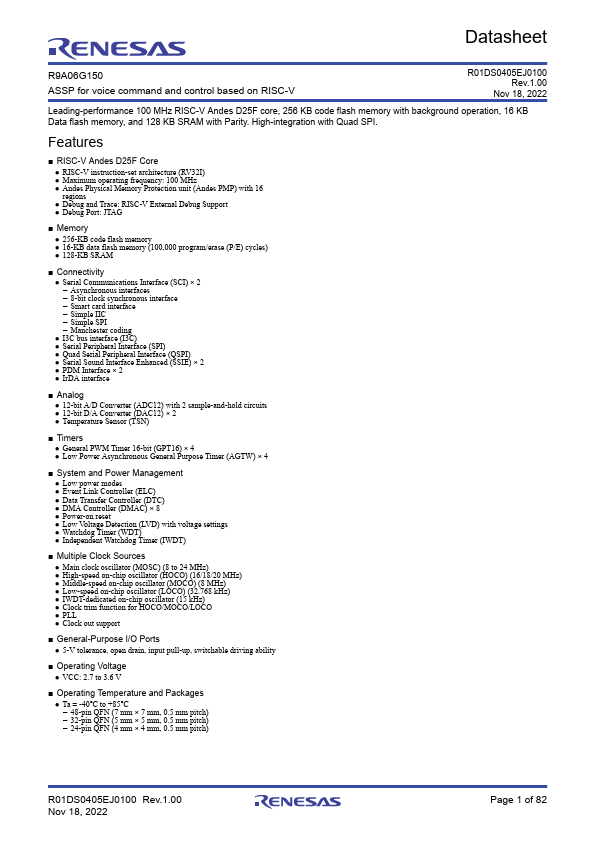

R9A06G150

Overview

- RISC-V Andes D25F Core

- RISC-V instruction-set architecture (RV32I)

- Maximum operating frequency: 100 MHz

- Andes Physical Memory Protection unit (Andes PMP) with 16 regions

- Debug and Trace: RISC-V External Debug Support

- Debug Port: JTAG

- Memory

- 256-KB code flash memory

- 16-KB data flash memory (100,000 program/erase (P/E) cycles)

- 128-KB SRAM