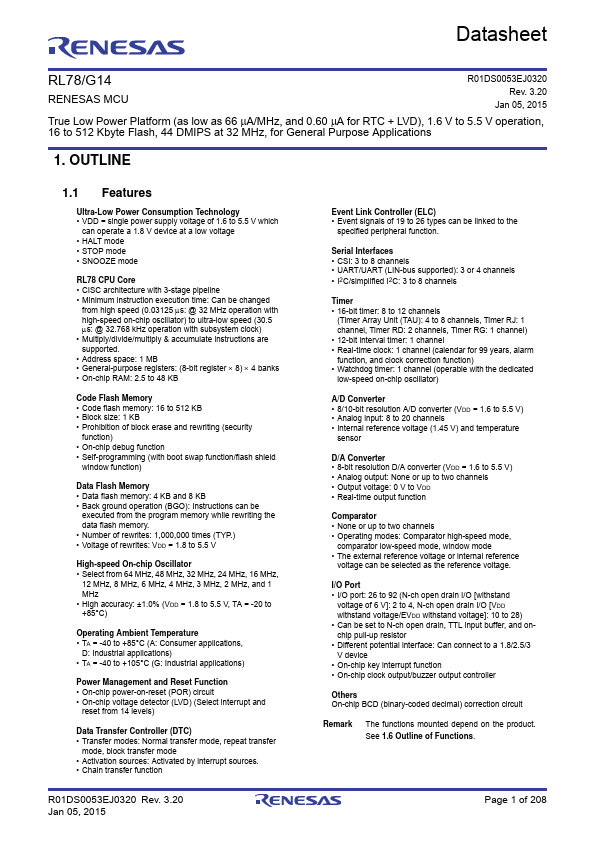

| Part | RL78G14 |

|---|---|

| Description | MCU |

| Manufacturer | Renesas |

| Size | 2.30 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HFDOM40B-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |

| CP2105 | Silicon Labs | SINGLE-CHIP USB TO DUAL UART BRIDGE |

| HFDOM44P-xxxSx | Hanbit Electronics | 44Pin Flash Disk Module |