SR5015-80 Overview

Description

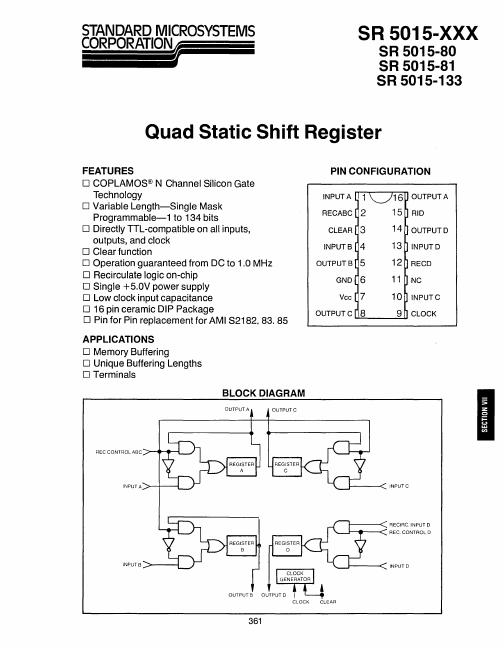

The SMC SR 5015-XXX is a quad static shift register family fabricated using SMC's COPLAMOS@ N channel silicon gate process which provides a higher functional density and speed on a monolithic chip than conventional MaS technology. The COPLAMOS® process provides high speed operation, low power dissipation, low clock input capacitance, and single +5 volt power supply operation.