M74HC259

M74HC259 is 8 BIT ADDRESSABLE LATCH manufactured by STMicroelectronics.

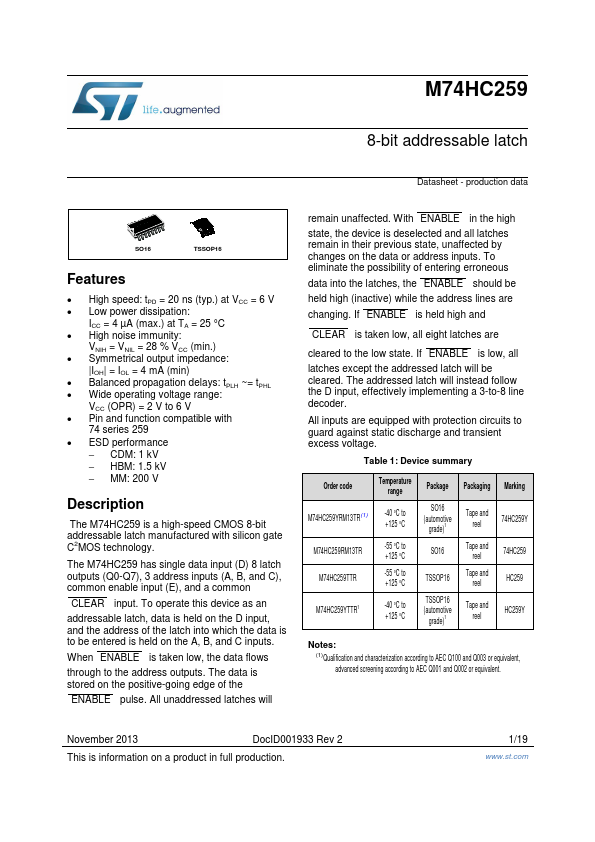

DESCRIPTION

The M54/74HC259 is a high speed CMOS 8 BIT ADDRESSABLE LATCH fabricated in silicon gate C2MOS technology. It has the same high speed performance of LSTTL bined with true CMOS low power consumption. The M54HC259/M74HC259 has single data input (D) 8 latch outputs (Q0-Q7), 3 address inputs (A, B, and C), mon enable input (E), and a mon CLEAR input. To operate this device as an addressable latch, data is held on the D input, and the address of the latch into which the data is to be entered is held on the A, B, and C inputs. When ENABLE is taken low the data flows through to the addresses output. The data is stored on the positive-going edge of the ENABLE pulse. All unaddressed latches will remain unaffected. With ENABLE in the high state the device is deselected and all latches remain in their previous state, unaffected by changes on the data or address inputs. To eliminate the possibility of entering erroneous data into the latches, the ENABLE should be held high (inactive) while the address lines are changing. If ENABLE is held high and CLEAR is taken low all eight latches are cleared to the low state. If ENABLE is low all latches except the addressed latch will be cleared. The addressed latch will instead follow the D input, effectively implementing a 3-to 8 line decoder. All inputs are equipped with protection circuits against static discharge and transient excess voltage.

October 1992

NC = No Internal Connection

PIN CONNECTIONS (top view)

1/12

M54/M74HC259

TRUTH TABLE

INPUTS CLEAR H H L L ENABLE L H L H OUTPUTS OF ADDRESSED LATCH D Qi0 D L EACH OTHER OUTPUT Qi0 Qi0 L L FUNCTION ADDRESSABLE LATCH MEMORY 8 LINE DEMULTIPLEXER CLEAR ALL BITS TO ’L’

D: The level at the data input Qi0: The level before the indicated steady state input conditions were established, (i = 0, 1, ,7).

SELECT INPUTS C L L L L H H H H B L L H H L L H H A L H L H L H L H

LATCH ADDRESSED Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

LOGIC DIAGRAM

2/12

M54/M74HC259

INPUT AND OUTPUT EQUIVALENT...