M74HC280 Description

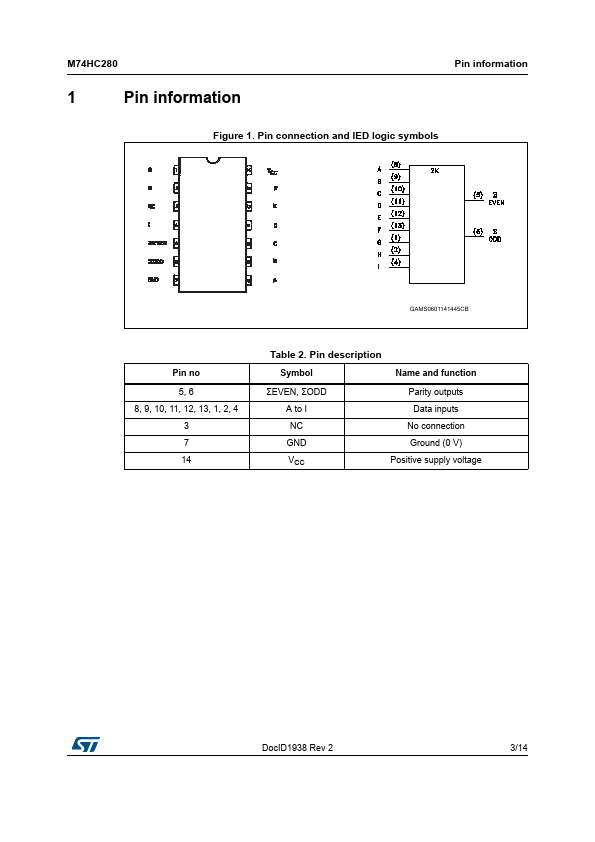

The M74HC280 is a high-speed CMOS 9-bit parity generator fabricated with silicon gate C2MOS technology. It is posed of nine data inputs (A to I) and odd/even parity outputs (ΣODD and ΣEVEN). The nine data inputs control the output conditions.

M74HC280 Key Features

- High-speed: tPD = 22 ns (typ.) at VCC = 6 V

- Low power dissipation: ICC = 4 μA (max.) at TA = 25 °C

- High noise immunity: VNIH = VNIH = 28 % VCC (min)

- Symmetrical output impedance: |IOH| = IOL = 4 mA (min.)

- Balanced propagation delays

- Wide operating voltage range: VCC (opr) = 2 V to 6 V

- Pin and function patible with 74 series 280

- ESD performance

- HBM: 2 kV

- MM: 200 V