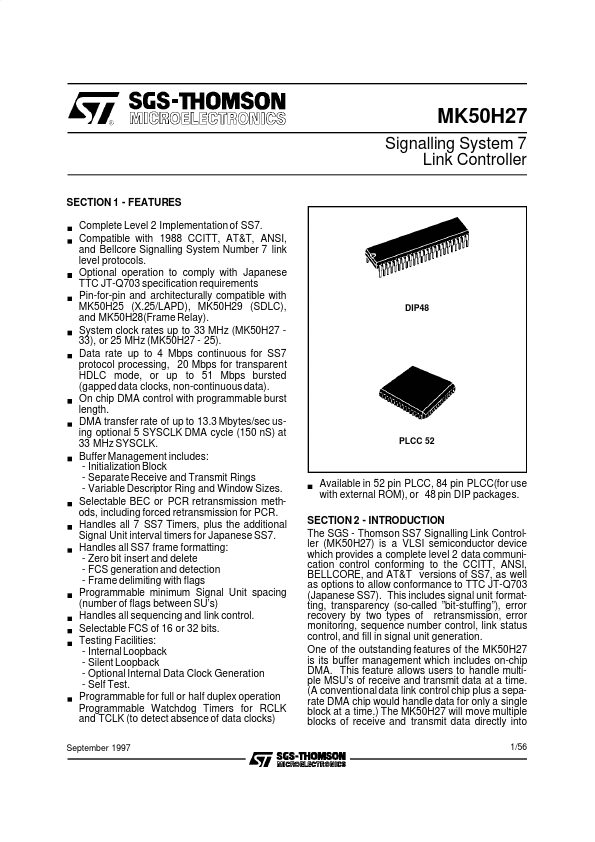

| Part | MK50H27 |

|---|---|

| Description | Signalling System 7 Link Controller |

| Manufacturer | STMicroelectronics |

| Size | 417.62 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| bq24780S | Texas Instruments | 1- to 4-Cell Hybrid Power Boost Mode Battery Charge Controller |

| DK112 | Dongke Semiconductor | High-performance switching power supply controller |

| LP3667 | LANDP | Simplified self-powered primary-side feedback controller |