ST20TP2BX50S

ST20TP2BX50S is Programmable Transport IC manufactured by STMicroelectronics.

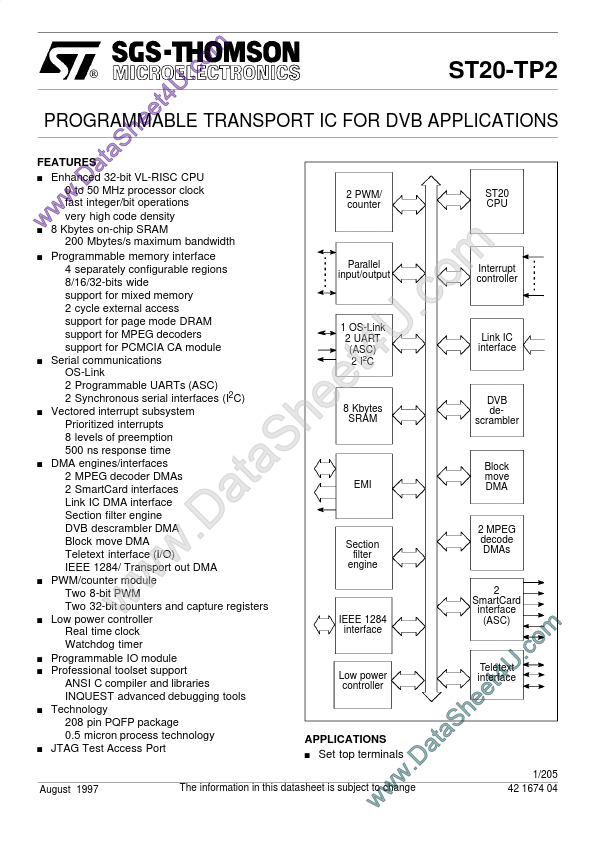

FEATURES s Enhanced 32-bit VL-RISC CPU 0 to 50 MHz processor clock fast integer/bit operations very high code density s 8 Kbytes on-chip SRAM 200 Mbytes/s maximum bandwidth s Programmable memory interface 4 separately configurable regions 8/16/32-bits wide support for mixed memory 2 cycle external access support for page mode DRAM support for MPEG decoders support for PCMCIA CA module s Serial munications OS-Link 2 Programmable UARTs (ASC) 2 Synchronous serial interfaces (I2C) s Vectored interrupt subsystem Prioritized interrupts 8 levels of preemption 500 ns response time s DMA engines/interfaces 2 MPEG decoder DMAs 2 Smart Card interfaces Link IC DMA interface Section filter engine DVB descrambler DMA Block move DMA Teletext interface (I/O) IEEE 1284/ Transport out DMA s PWM/counter module Two 8-bit PWM Two 32-bit counters and capture registers s Low power controller Real time clock Watchdog timer s Programmable IO module s Professional toolset support ANSI C piler and libraries INQUEST advanced debugging tools s Technology 208 pin PQFP package 0.5 micron process technology s JTAG Test Access Port w w at .D w h S a e

U 4 t m o .c

ST20-TP2

2 PWM/ counter

ST20 CPU

Parallel input/output

1 OS-Link 2 UART (ASC) 2 I2C w w w t a .D

S a e h

U 4 t e

.c m o

Interrupt controller

Link IC interface

8 Kbytes SRAM

DVB descrambler

Block move DMA

Section filter engine

2 MPEG decode DMAs

IEEE 1284 interface

2 Smart Card interface (ASC)

Low power controller

APPLICATIONS s Set top terminals

August 1997

The information in this datasheet is subject to change w w w

.D a

S a t e e h

Teletext interface

U 4 t m o .c

1/205 42 1674 04

ST20-TP2

Contents

1 2 Introduction

- -

- -

- -

- -

- -

- - ST20-TP2 architecture overview

- -

-...