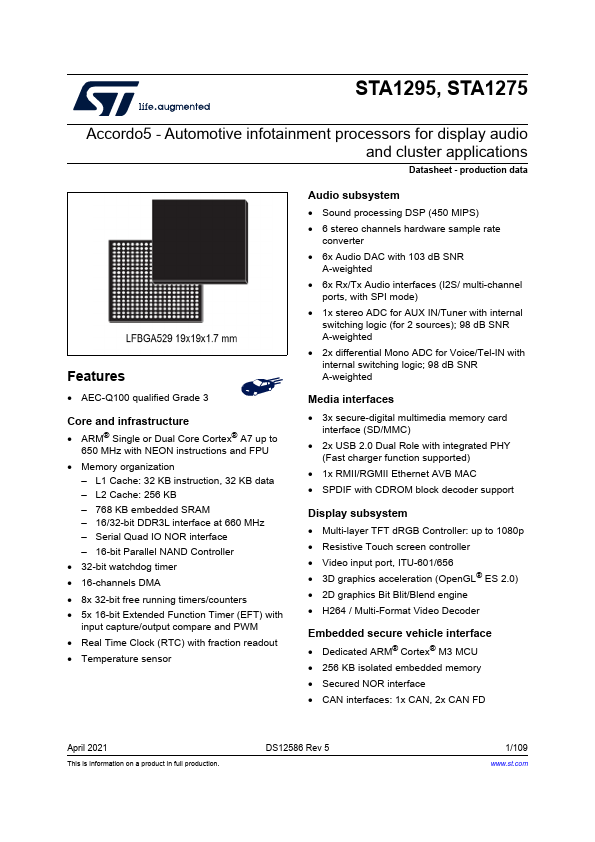

STA1295

Key Features

- AEC-Q100 qualified Grade 3 Core and infrastructure

- ARM® Single or Dual Core Cortex® A7 up to 650 MHz with NEON instructions and FPU

- 32-bit watchdog timer

- 16-channels DMA

- 8x 32-bit free running timers/counters

- Real Time Clock (RTC) with fraction readout

- Temperature sensor Audio subsystem

- Sound processing DSP (450 MIPS)

- 6 stereo channels hardware sample rate converter

- 6x Audio DAC with 103 dB SNR A-weighted