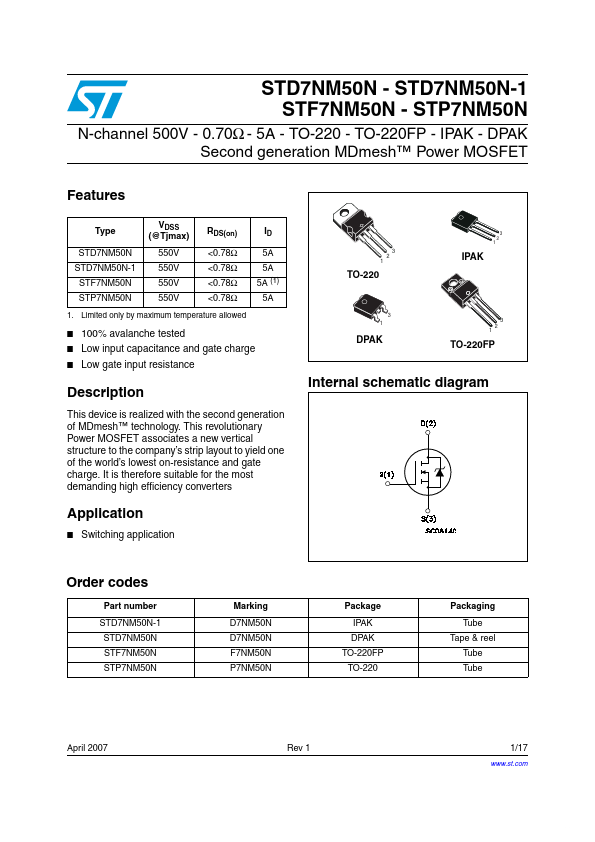

STP7NM50N Overview

This device is realized with the second generation of MDmesh™ technology. This revolutionary Power MOSFET associates a new vertical structure to the pany’s strip layout to yield one of the world’s lowest on-resistance and gate charge. 4 2.1 (curves) ............................

STP7NM50N Key Features

- 100% avalanche tested Low input capacitance and gate charge Low gate input resistance

- Switching application

- http://..net/

- STD7NM50N-1

- STF7NM50N

- STP7NM50N

- 3 Electrical characteristics

- 10 Packaging mechanical data

- 15 Revision history

- http://..net/