Datasheet Summary

Gre r Pro

Ver 2.0

S a mHop Microelectronics C orp.

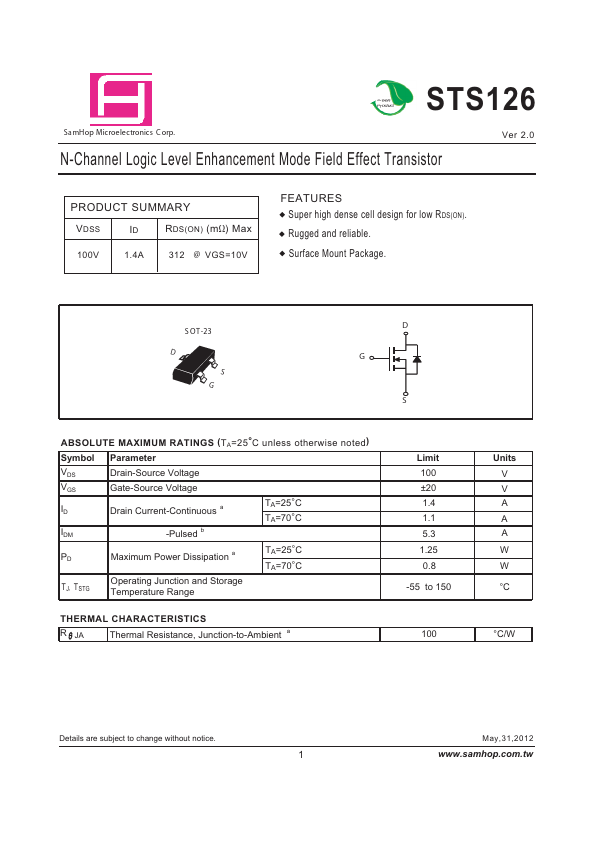

N-Channel Logic Level Enhancement Mode Field Effect Transistor

PRODUCT SUMMARY

V DSS

100V

Features

Super high dense cell design for low R DS(ON). Rugged and reliable. Surface Mount Package.

1.4A

R DS(ON) (m Ω) Max

312 @ VGS=10V

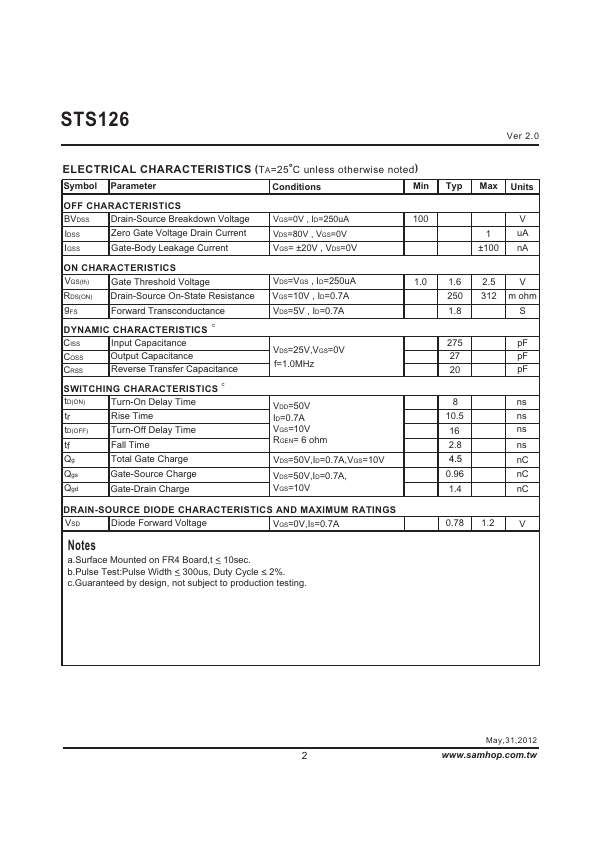

S...