K7D321874A Description

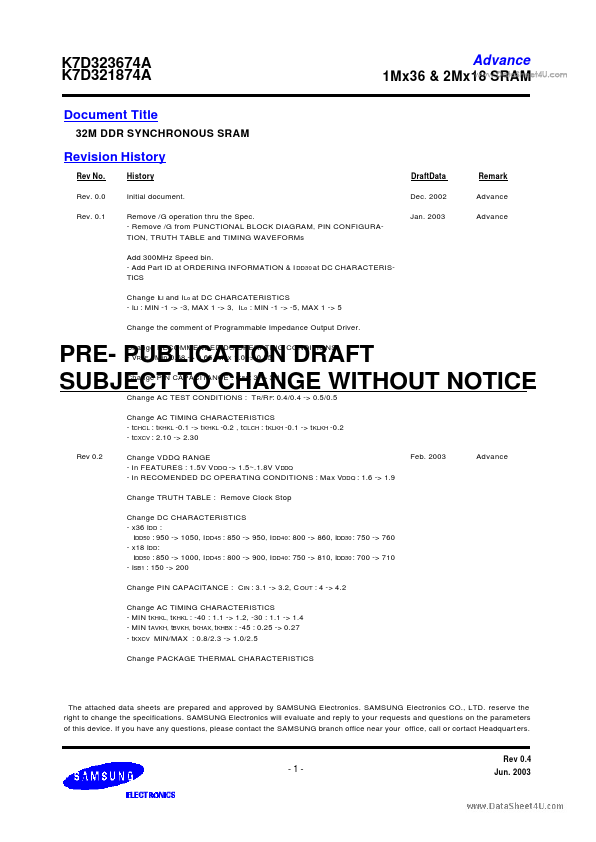

K7D323674A K7D321874A Document Title 32M DDR SYNCHRONOUS SRAM Advance .. 1Mx36 & 2Mx18 SRAM Revision History Rev No. 0.1 History Initial document.

K7D321874A Key Features

- In REENDED DC OPERATING CONDITIONS : Max VDDQ : 1.6 -> 1.9 Change TRUTH TABLE : Remove Clock Stop Change DC CHARACTERIST

- ISB1 : 150 -> 200 Change PIN CAPACITANCE : C IN : 3.1 -> 3.2, C OUT : 4 -> 4.2 Change AC TIMING CHARACTERISTICS

- MIN t KHKL, tKHKL : -40 : 1.1 -> 1.2, -30 : 1.1 -> 1.4

- MIN t AVKH, tBVKH, tKHAX, tKHBX : -45 : 0.25 -> 0.27

- tKXCV MIN/MAX : 0.8/2.3 -> 1.0/2.5 Change PACKAGE THERMAL CHARACTERISTICS Feb. 2003 Advance

- VREF : Min 0.68 -> 0.65, Max 1.0 -> 0.85

- ISB1 : 200 -> 300 Change 300Mhz speed bin to 333Mhz

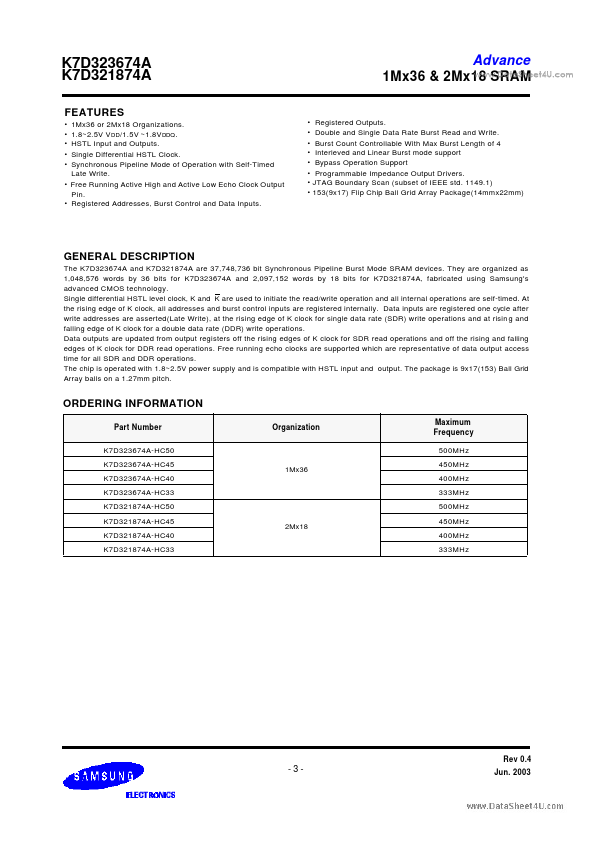

- 1Mx36 or 2Mx18 Organizations. 1.8~2.5V V DD/1.5V ~1.8V DDQ . HSTL Input and Outputs. Single Differential HSTL Clock. Syn

- Free Running Active High and Active Low Echo Clock Output Pin

- Registered Addresses, Burst Control and Data Inputs