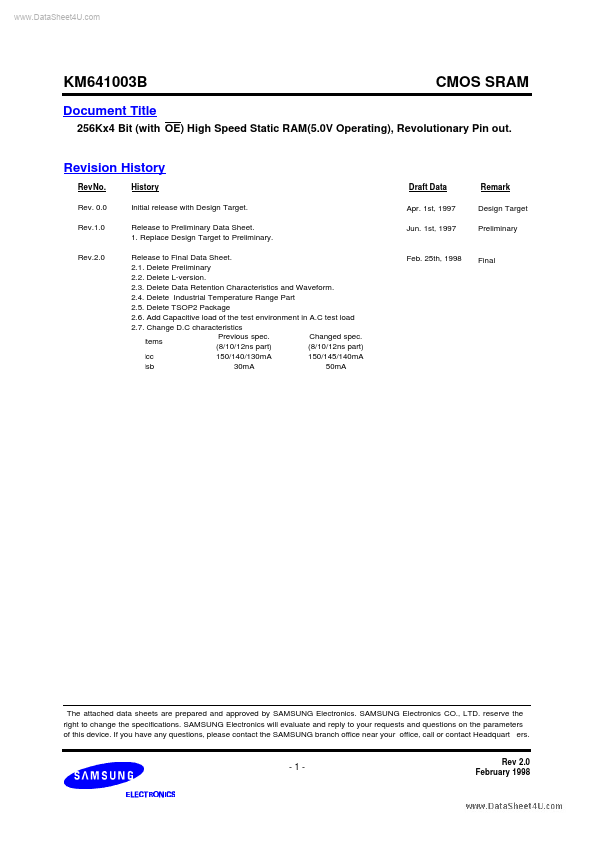

KM641003B

KM641003B is CMOS SRAM manufactured by Samsung Semiconductor.

FEATURES

- Fast Access Time 8,10,12ns(Max.)

- Low Power Dissipation Standby (TTL) : 50 m A(Max.) (CMOS) : 10 m A(Max.) Operating KM641003B

- 8 : 150 m A(Max.) KM641003B

- 10 : 145 m A(Max.) KM641003B

- 12 : 140 m A(Max.)

- Single 5.0V ±10% Power Supply

- TTL patible Inputs and Outputs

- I/O patible with 3.3V Device

- Fully Static Operation

- No Clock or Refresh required

- Three State Outputs

- Center Power/Ground Pin Configuration

- Standard Pin Configuration KM641003BJ : 32-SOJ-400

Preliminary PRELIMINARY CMOS SRAM

GENERAL DESCRIPTION

The KM641003B is a 1,048,576-bit high-speed Static Random Access Memory organized as 262,144 words by 4 bits. The KM641003B uses 4 mon input and output lines and has an output enable pin which operates faster than address access time at read cycle. The device is fabricated using SAMSUNG ′s advanced CMOS process and designed for high-speed circuit technology. It is particularly well suited for use in high-density high-speed system applications. The KM641003B is packaged in a 400 mil 32-pin plastic SOJ.

PIN CONFIGURATION (Top View)

N.C. A0 A1

1 2 3 4 5 6 7 8 9

32 A17 31 A16 30 A15 29 A14 28 A13 27 OE

FUNCTIONAL BLOCK DIAGRAM

A2 A3 CS

Clk Gen.

A0 A1 A2 A3 A4 A5 A6 A7

Pre-Charge Circuit

I/O1 Vcc Vss

26 I/O4

25 Vss 24 Vcc 23 I/O3 22 A12 21 A11 20 A10 19 18 A9 A8

I/O2 10

Row Select

WE 11

Memory Array 256 Rows 1024x4 Columns

A4 A5 A6 A7

12 13 14 15

N.C. 16 I/O1 ~ I/O4

17 N.C.

Data Cont. CLK Gen.

I/O Circuit & Column...