EM9010 Overview

Key Specifications

Description

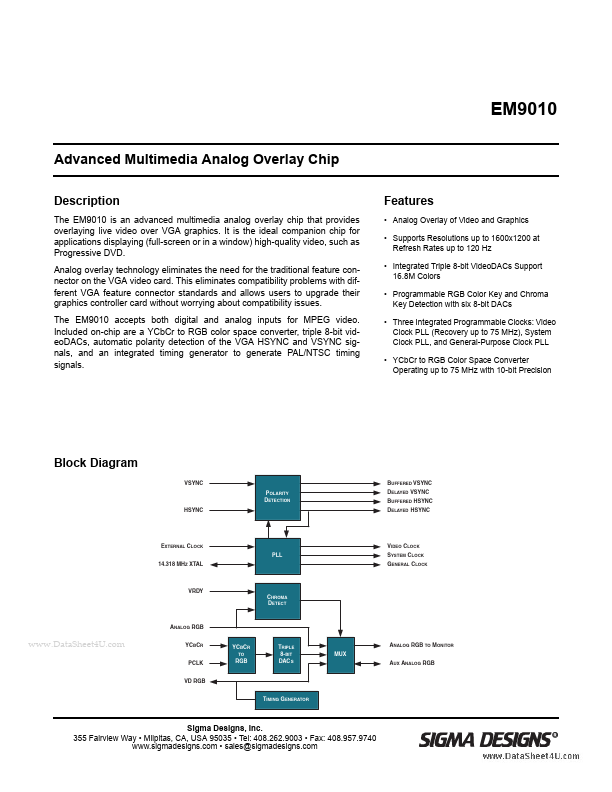

The EM9010 is an advanced multimedia analog overlay chip that provides overlaying live video over VGA graphics. It is the ideal companion chip for applications displaying (full-screen or in a window) high-quality video, such as Progressive DVD.

Key Features

- Analog Overlay of Video and Graphics

- Supports Resolutions up to 1600x1200 at Refresh Rates up to 120 Hz

- Integrated Triple 8-bit VideoDACs Support 16.8M Colors

- Programmable RGB Color Key and Chroma Key Detection with six 8-bit DACs

- Three Integrated Programmable Clocks: Video Clock PLL (Recovery up to 75 MHz), System Clock PLL, and General-Purpose Clock PLL