82S10

DESCRIPTION

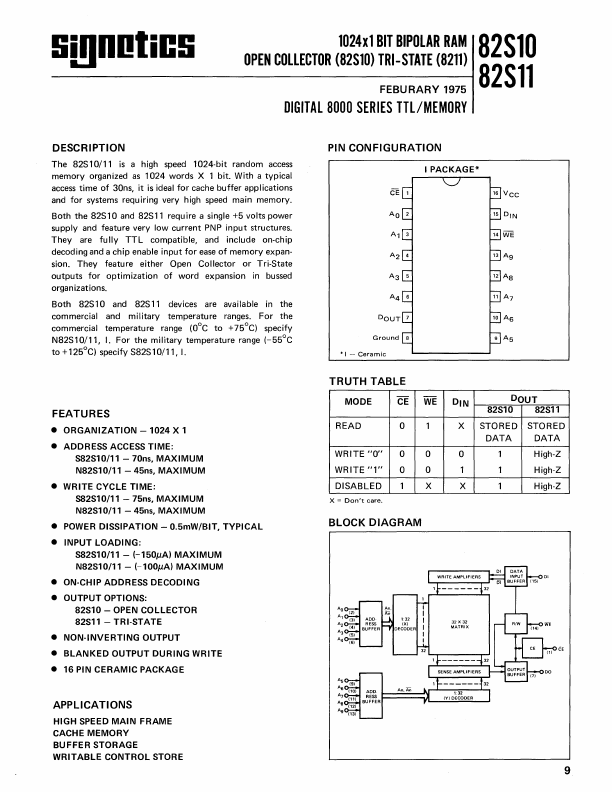

The 82S10/11 is a high speed 1024-bit random access memory organized as 1024 words X 1 bit. With a typical access time of 30ns, it is ideal for cache buffer applications and for systems requiring very high speed main memory. Both the 82S10 and 82S11 require a single +5 volts power supply and feature very low current PNP input structures. They are fully TTL patible, and include on-chip decoding and a chip enable input for ease of memory expansion. They feature either Open Collector or Tri-State outputs for optimization of word expansion in bussed organ izations. Both 82S 10 and 82S 11 devices are available in the mercial and military temperature ranges. For the mercial temperature range (Oo C to +75°C) specify N82S10/11, I. For the military temperature range (-55°C to + 125°C) specify S82S 10/11, I.

FEATURES

- ORGANIZATION

- 1024 X 1

- ADDRESS ACCESS TIME:

S82S10/11

- 70n5, MAXIMUM N82S10/11

- 45ns, MAXIMUM

- WRITE CYCLE TIME: S82S10/11

- 75n5, MAXIMUM N82S10/11

- 45n5,...