SiS5571

SiS5571 is Pentium PCI/ISA Chipset manufactured by Silicon Integrated System.

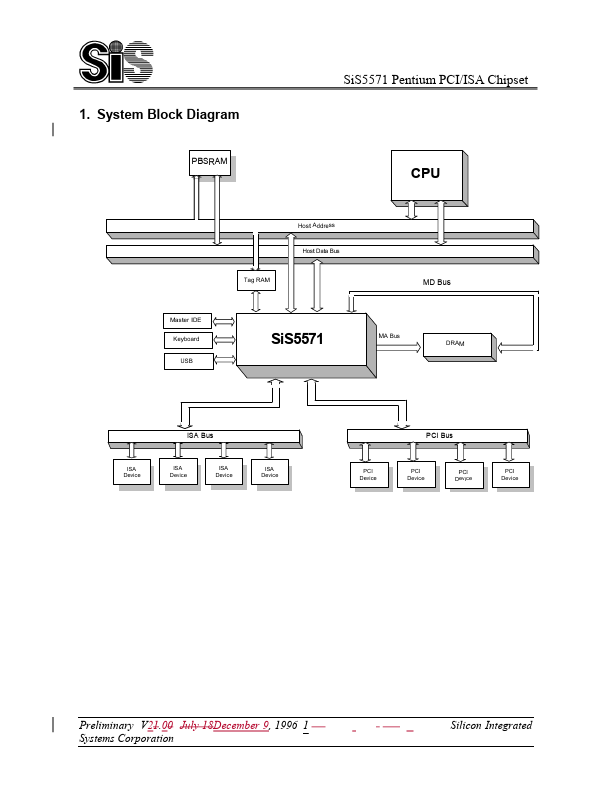

1. System Block Diagram

PBSRAM

SiS5571 Pentium PCI/ISA Chipset CPU

Master IDE Keyboard USB

Tag RAM

Host Address Host Data Bus

MD Bus

MA Bus

DRAM

ISA Device

ISA Bus

ISA Device

ISA Device

ISA Device

PCI Bus

PCI Device

PCI Device

PCI Device

PCI Device

Preliminary V21.00 July 18December 9, 1996 1 Systems Corporation

Silicon Integrated

SiS5571 Pentium PCI/ISA Chipset

2. Features

- Supports Intel Pentium CPU and other patible CPU at 75/66/60/50MHz

(external clock speed)

- Supports the Pipelined Address Mode of Pentium CPU

- Supports the Full 64-bit Pentium Processor data Bus

- Supports 32-bit PCI Interface

- Integrated Second Level ( L2 ) Cache Controller

- Write...