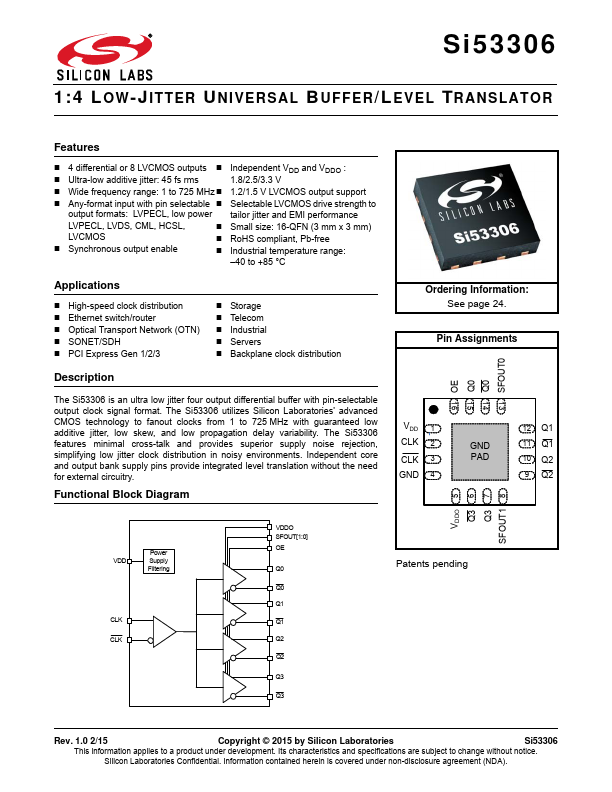

SI53306

Overview

The Si53306 is an ultra low jitter four output differential buffer with pin-selectable output clock signal format. The Si53306 utilizes Silicon Laboratories' advanced CMOS technology to fanout clocks from 1 to 725 MHz with guaranteed low additive jitter, low skew, and low propagation delay variability.

- 4 differential or 8 LVCMOS outputs

- Independent VDD and VDDO :

- Ultra-low additive jitter: 45 fs rms

- 8/2.5/3.3 V

- Wide frequency range: 1 to 725 MHz

- 1.2/1.5 V LVCMOS output support

- Any-format input with pin selectable

- Selectable LVCMOS drive strength to output formats: LVPECL, low power tailor jitter and EMI performance