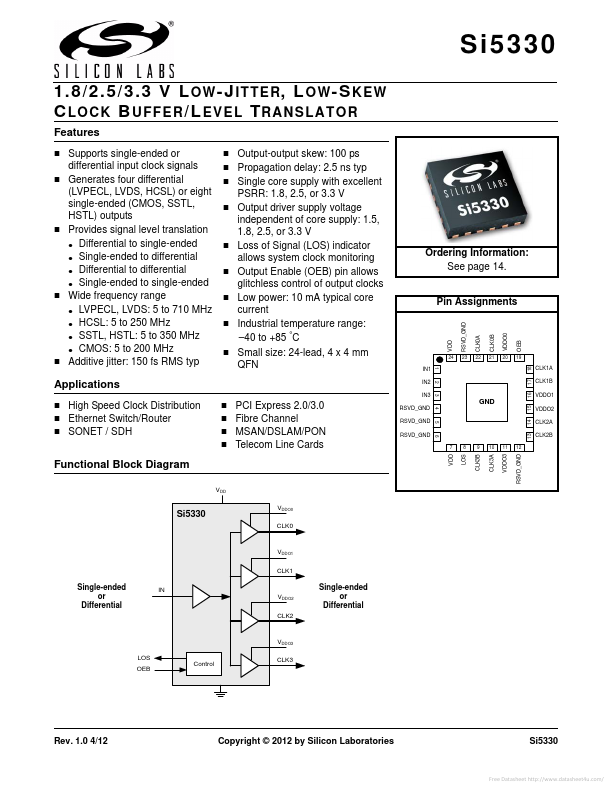

SI5330

Overview

- 18 17 16 15 14 13 7 8 9 10 11 12

- Supports single-ended or differential input clock signals Generates four differential (LVPECL, LVDS, HCSL) or eight single-ended (CMOS, SSTL, HSTL) outputs Provides signal level translation

- Differential to single-ended

- Single-ended to differential

- Differential to differential

- Single-ended to single-ended Wide frequency range

- LVPECL, LVDS: 5 to 710 MHz

- HCSL: 5 to 250 MHz

- SSTL, HSTL: 5 to 350 MHz

- CMOS: 5 to 200 MHz Additive jitter: 150 fs RMS typ * * * * * * *