SL23EP08 Overview

Description

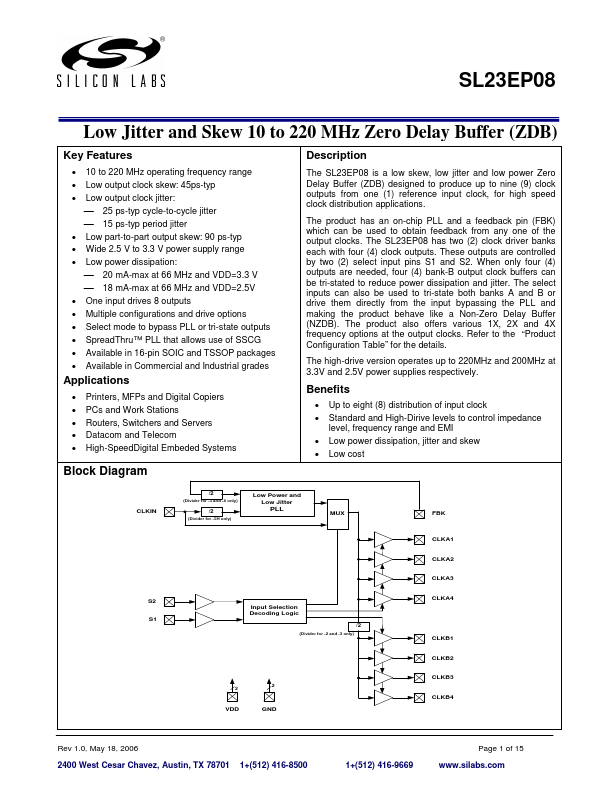

The SL23EP08 is a low skew, low jitter and low power Zero Delay Buffer (ZDB) designed to produce up to nine (9) clock outputs from one (1) reference input clock, for high speed clock distribution applications. The product has an on-chip PLL and a feedback pin (FBK) which can be used to obtain feedback from any one of the output clocks.

Key Features

- 10 to 220 MHz operating frequency range

- Low output clock skew: 45ps-typ

- Low output clock jitter: 25 ps-typ cycle-to-cycle jitter 15 ps-typ period jitter

- Low part-to-part output skew: 90 ps-typ

- Wide 2.5 V to 3.3 V power supply range

- Low power dissipation: 20 mA-max at 66 MHz and VDD=3.3 V 18 mA-max at 66 MHz and VDD=2.5V

- One input drives 8 outputs

- Multiple configurations and drive options

- Select mode to bypass PLL or tri-state outputs

- SpreadThru™ PLL that allows use of SSCG