SSPL6040D Overview

Description

These N-Channel enhancement mode power field effect transistors are produced using silikron proprietary MOSFET technology. This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode.

Key Features

- Advanced Process Technology

- Special designed for PWM, load switching and general purpose applications

- Ultra low on-resistance with low gate charge

- Fast switching and reverse body recovery

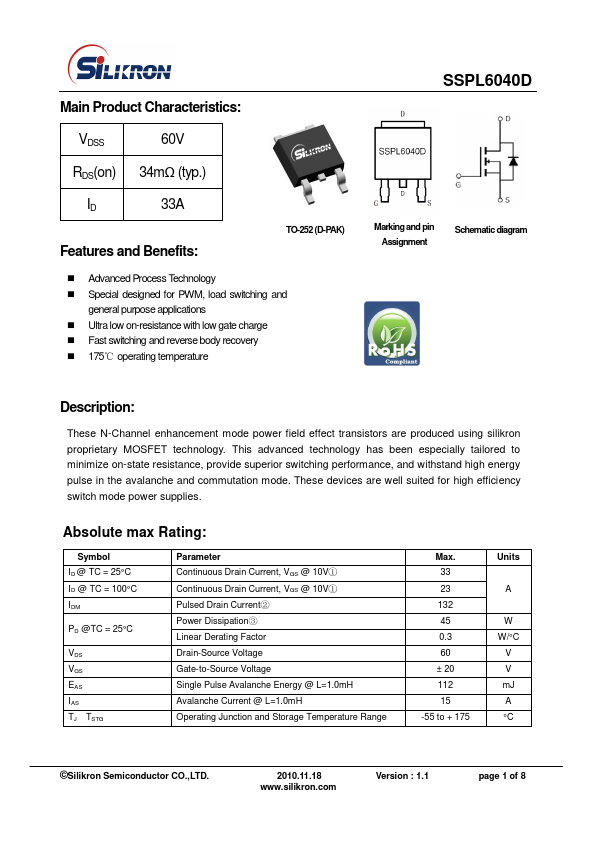

- 175℃ operating temperature SSPL6040D Marking and pin Assignment