TC58DVM82A1FT00

TC58DVM82A1FT00 is 256-MBIT (32M x 8 BITS) CMOS NAND E2PROM manufactured by Toshiba.

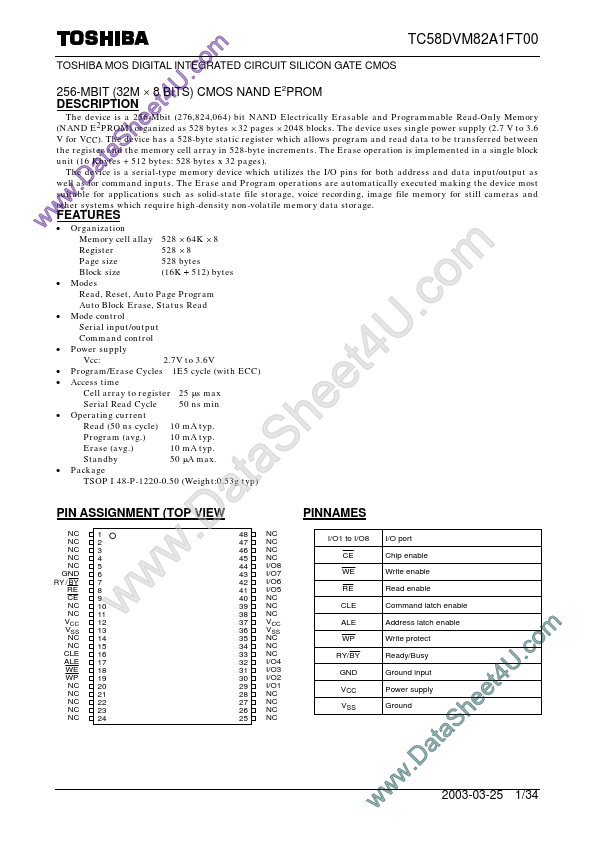

m o TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS .c U CMOS NAND E PROM 256-MBIT (32M × 8 BITS) 4 t DESCRIPTION e e h S a at .D w w Features w

The device is a 256-Mbit (276,824,064) bit NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as 528 bytes × 32 pages × 2048 blocks. The device uses single power supply (2.7 V to 3.6 V for VCC). The device has a 528-byte static register which allows program and read data to be transferred between the register and the memory cell array in 528-byte increments. The Erase operation is implemented in a single block unit (16 Kbytes + 512 bytes: 528 bytes x 32 pages). The device is a...