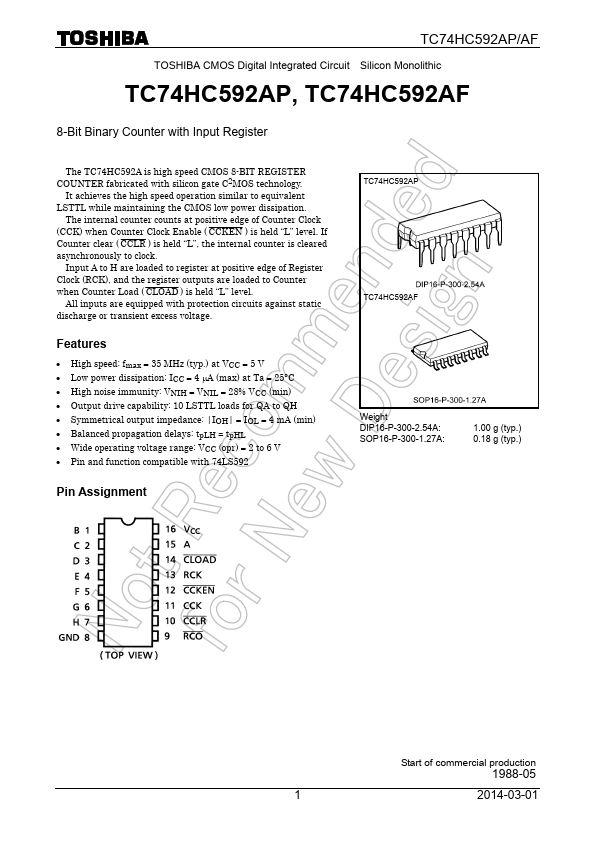

TC74HC592AP

TC74HC592AP is 8-Bit Binary Counter manufactured by Toshiba.

- Part of the TC74HC592AF comparator family.

- Part of the TC74HC592AF comparator family.

TC74HC592AP/AF

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74HC592AP, TC74HC592AF

8-Bit Binary Counter with Input Register

The TC74HC592A is high speed CMOS 8-BIT REGISTER COUNTER fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.

The internal counter counts at positive edge of Counter Clock (CCK) when Counter Clock Enable ( CCKEN ) is held “L” level. If Counter clear ( CCLR ) is held “L”, the internal counter is cleared asynchronously to clock.

Input A to H are loaded to register at positive edge of Register Clock (RCK), and the register outputs are loaded to...