TC74HC74AFN

TC74HC74AFN is CMOS Digital Integrated Circuit Silicon Monolithic Dual D-Type Flip Flop Preset and Clear manufactured by Toshiba.

- Part of the TC74HC74AF comparator family.

- Part of the TC74HC74AF comparator family.

TC74HC74AP/AF/AFN

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

..

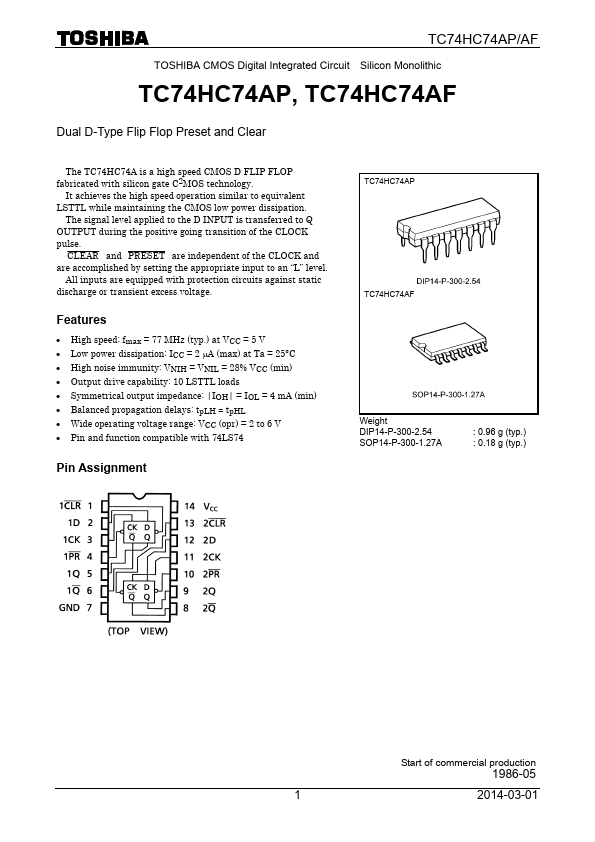

TC74HC74AP,TC74HC74AF,TC74HC74AFN

Dual D-Type Flip Flop Preset and Clear

The TC74HC74A is a high speed CMOS D FLIP FLOP fabricated with silicon gate C2MOS technology. It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation. The signal level applied to the D INPUT is transferred to Q OUTPUT during the positive going transition of the CLOCK pulse. CLEAR and PRESET are independent of the CLOCK and are acplished by setting the appropriate input to an “L” level. All inputs are equipped with protection circuits against static discharge or...