Datasheet Summary

Description

4 (word x bit x bank), respectively.

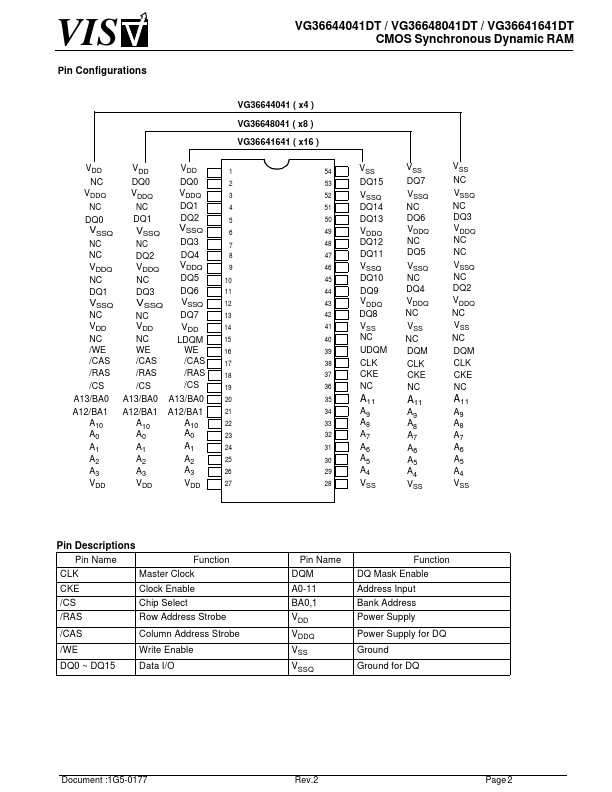

VG36644041DT / VG36648041DT / VG36641641DT CMOS Synchronous Dynamic RAM

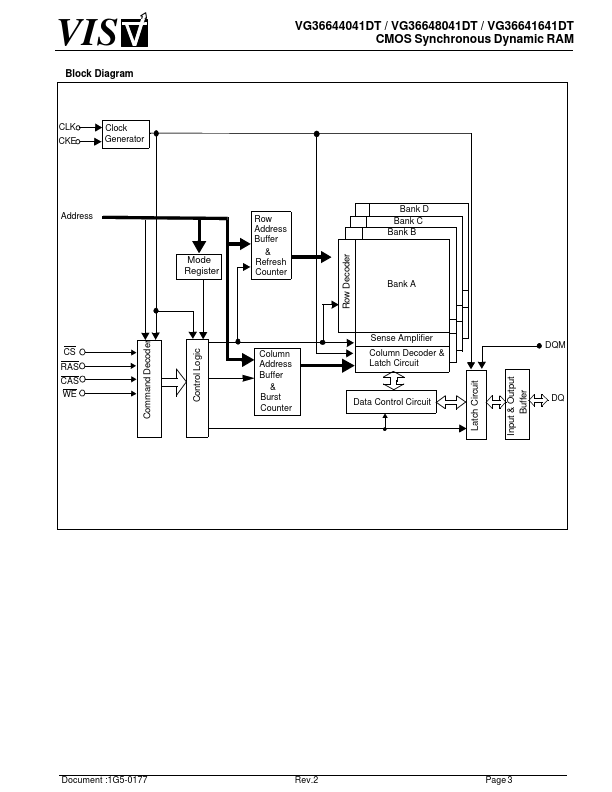

The VG36644041D, VG36648041D and VG36641641D are high-speed 67,108,864-bit synchronous dynamic random-access memories, organized as 4,194,304 x 4 x 4, 2,097,152 x 8 x 4 and 1,048,576 x 16 x

The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture. All input and outputs are synchronized with the positive edge of the clock.The synchronous DRAMs are patible with Low Voltage TTL (LVTTL).These products are packaged in 54-pin TSOPII.

Features

- Single 3.3V ( ± 0.3V ) power supply

- High speed clock cycle time -6 : 166MHz<3-3-3>,...