SI7464DP

DESCRIPTION

The attached spice model describes the typical electrical characteristics of the n-channel vertical DMOS. The subcircuit model is extracted and optimized over the

- 55 to 125°C temperature ranges under the pulsed 0 to 10V gate drive. The saturated output impedance is best fit at the gate bias near the threshold voltage. A novel gate-to-drain feedback capacitance network is used to model the gate charge characteristics while avoiding convergence difficulties of the switched Cgd model. All model parameter values are optimized to provide a best fit to the measured electrical data and are not intended as an exact physical interpretation of the device.

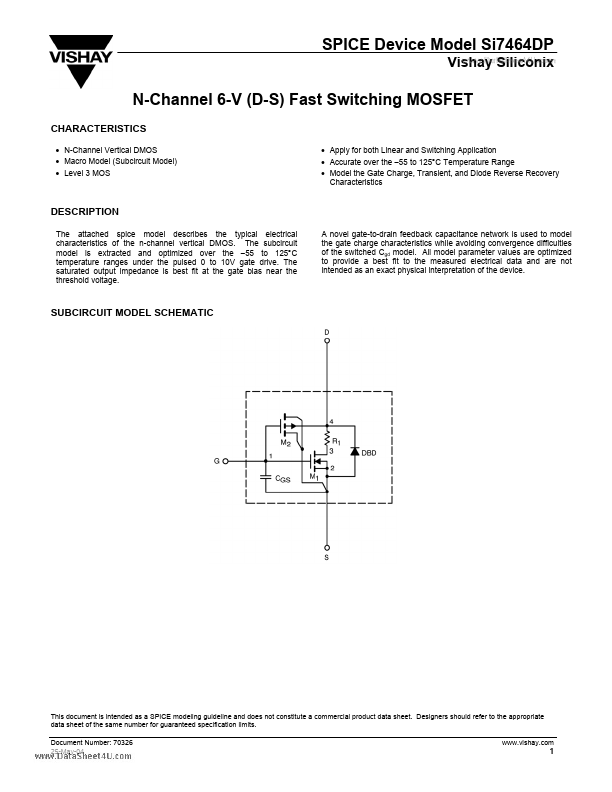

SUBCIRCUIT MODEL SCHEMATIC

This document is intended as a SPICE modeling guideline and does not constitute a mercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits. Document Number: 70326 25-May-04 .vishay.

SPICE Device Model Si7464DP

Vishay...