W3H32M64E-XSBX

W3H32M64E-XSBX is 32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package manufactured by White Electronic Designs.

White Electronic Designs

ADVANCED- ..

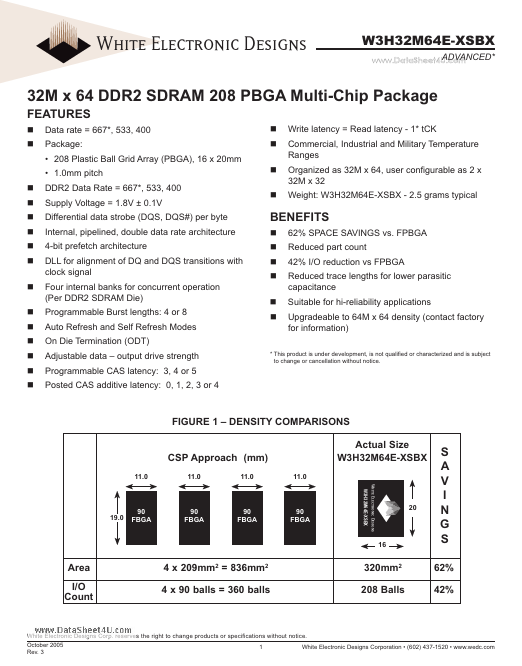

32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package

Features

Data rate = 667- , 533, 400 Package:

- 208 Plastic Ball Grid Array (PBGA), 16 x 20mm

- 1.0mm pitch DDR2 Data Rate = 667- , 533, 400 Supply Voltage = 1.8V ± 0.1V Differential data strobe (DQS, DQS#) per byte Internal, pipelined, double data rate architecture 4-bit prefetch architecture DLL for alignment of DQ and DQS transitions with clock signal Four internal banks for concurrent operation (Per DDR2 SDRAM Die) Programmable Burst lengths: 4 or 8 Auto Refresh and Self Refresh Modes On Die Termination (ODT) Adjustable data

- output drive strength Programmable CAS...