WV3EG265M64EFSU-D4

WV3EG265M64EFSU-D4 is 1GB- 2x64Mx64 DDR SDRAM UNBUFFERED manufactured by White Electronic Designs.

FEATURES

Double-data-rate architecture PC2700 and PC2100 Bi-directional data strobes (DQS) Differential clock inputs (CK & CK#) Programmable Read Latency 2, 2.5 (clock) Programmable Burst Length (2,4,8) Programmable Burst type (sequential & interleave) Auto and self refresh, (8K/64ms refresh) Serial presence detect with EEPROM Power supply: VCC/VCCQ: 2.5V ± 0.2V Dual Rank 200 pin SO-DIMM package

- Package height options: D4: 31.75 mm (1.25”)

- This product is subject to change without notice.

DESCRIPTION

The WV3EG265M64EFSU is a 2x64Mx64 Double Data Rate SDRAM memory module based on 512Mb DDR SDRAM ponent. The module consists of sixteen 64Mx8 bit with 4 banks DDR SDRAMs in FBGA packages mounted on a 200 pin substrate. Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges and Burst Lengths allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

NOTE: Consult factory for availability of:

- Ro HS pliant products

- Vendor source control options

- Industrial temperature option

..

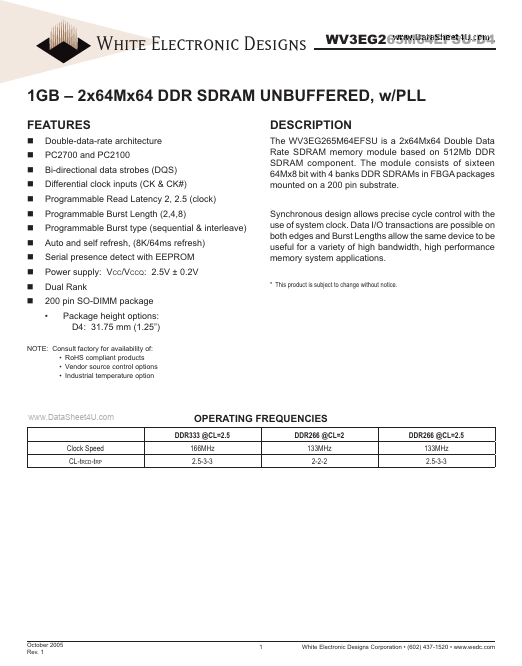

OPERATING FREQUENCIES

DDR333 @CL=2.5 DDR266 @CL=2 133MHz 2-2-2 DDR266 @CL=2.5 133MHz 2.5-3-3 166MHz 2.5-3-3

Clock Speed CL-t RCD-t RP

October 2005 Rev. 1

White Electronic Designs Corporation

- (602) 437-1520

- .wedc.

White Electronic Designs

PIN CONFIGURATION

PIN# SYMBOL PIN# SYMBOL PIN# 1 VREF 51 VSS 101 2 VREF 52 VSS 102 53 DQ19 103 3 VSS 4 VSS 54 DQ23 104 5 DQ0 55 DQ24 105 6 DQ4 56 DQ28 106 7 DQ1 57 VCC 107 8 DQ5 58 VCC 108 59 DQ25 109 9 VCC 10 VCC 60 DQ29 110 11 DQS0 61 DQS3 111 12 DM0 62 DM3 112 13 DQ2 63 VSS 113 14 DQ6 64 VSS 114 65 DQ26 115 15 VSS 16 VSS 66 DQ30 116 17 DQ3 67 DQ27 117 18 DQ7 68 DQ31 118 19 DQ8 69 VCC 119 20 DQ12 70 VCC 120 21 VCC 71 NC 121 72 NC 122 22 VCC 23 DQ9 73 NC 123 24 DQ13 74 NC 124 25 DQS1 75 VSS 125 126 26 DM1 76 VSS 27 VSS 77 NC 127 78 NC 128 28 VSS 29 DQ10 79 NC 129 30 DQ14 80 NC 130 .. 31 DQ11 81 VCC 131 32 DQ15 82 VCC 132...