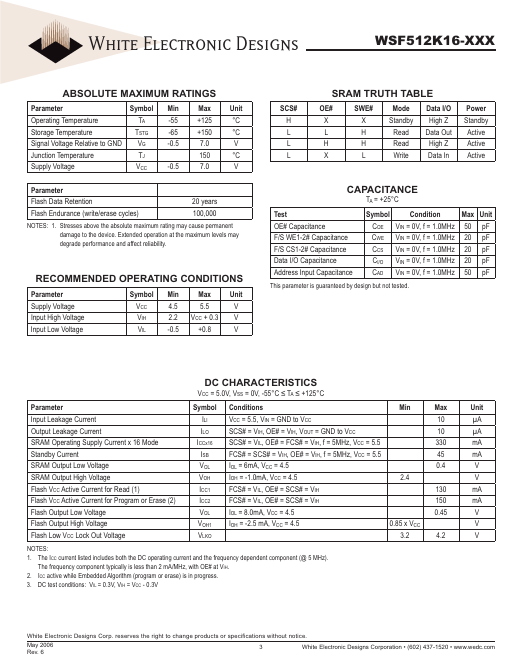

Datasheet Summary

..

White Electronic Designs

512KX16 SRAM/FLASH MODULE, SMD 5962-96901

Features

Access Times of 35ns (SRAM) and 90ns (FLASH) Access Times of 70ns (SRAM) and 120ns (FLASH) Packaging

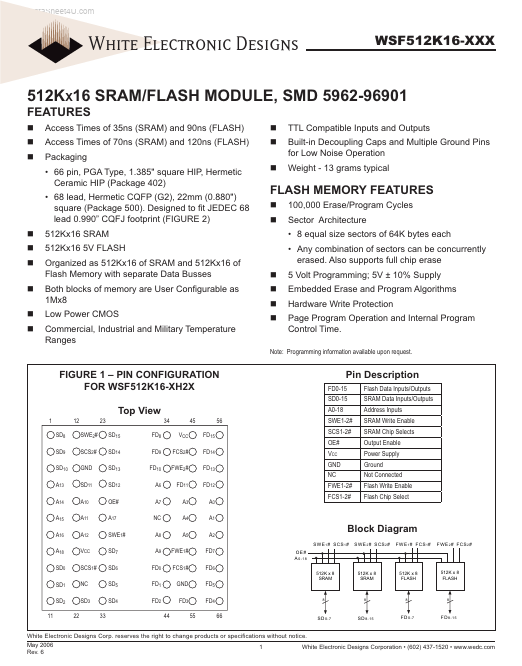

- 66 pin, PGA Type, 1.385" square HIP, Hermetic Ceramic HIP (Package 402)

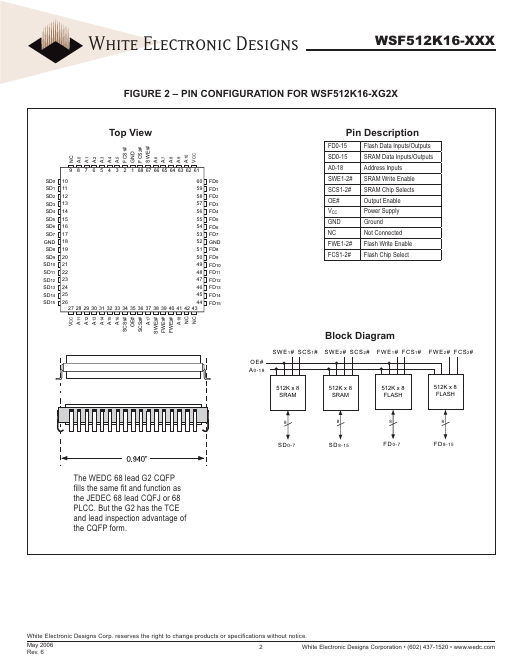

- 68 lead, Hermetic CQFP (G2), 22mm (0.880") square (Package 500). Designed to fit JEDEC 68 lead 0.990” CQFJ footprint (FIGURE 2) 512Kx16 SRAM 512Kx16 5V FLASH Organized as 512Kx16 of SRAM and 512Kx16 of Flash Memory with separate Data Busses Both blocks of memory are User Configurable as 1Mx8 Low Power CMOS mercial, Industrial and Military Temperature Ranges TTL patible Inputs and Outputs Built-in...