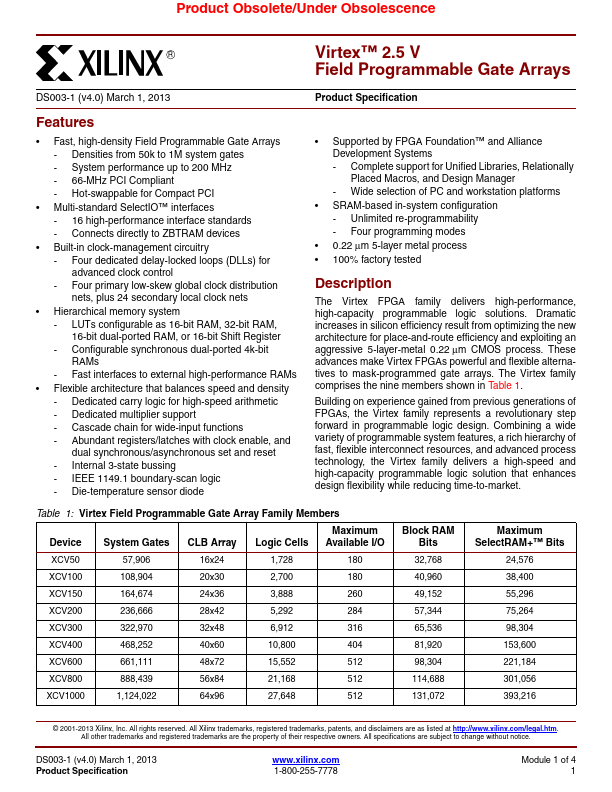

XCV50

Features

- Fast, high-density Field-Programmable Gate Arrays

- Densities from 50k to 1M system gates

- System performance up to 200 MHz

- 66-MHz PCI pliant

- Hot-swappable for pact PCI Multi-standard Select IO™ interfaces

- 16 high-performance interface standards

- Connects directly to ZBTRAM devices Built-in clock-management circuitry

- Four dedicated delay-locked loops (DLLs) for advanced clock control

- Four primary low-skew global clock distribution nets, plus 24 secondary local clock nets Hierarchical memory system

- LUTs configurable as 16-bit RAM, 32-bit RAM, 16-bit dual-ported RAM, or 16-bit Shift Register

- Configurable synchronous dual-ported 4k-bit RAMs

- Fast interfaces to external high-performance RAMs Flexible architecture that balances speed and density

- Dedicated carry logic for high-speed arithmetic

- Dedicated multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with clock enable, and dual synchronous/asynchronous set and reset

-...