XCV50E

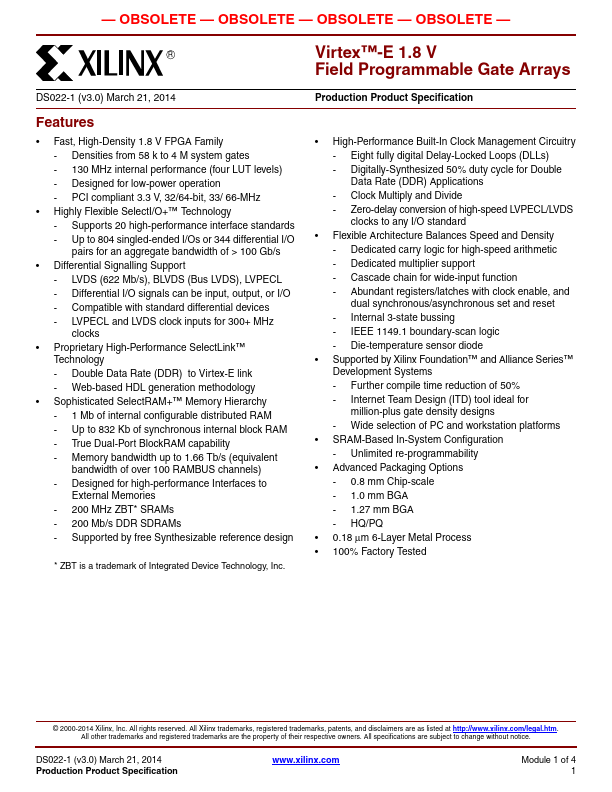

Features

- Fast, High-Density 1.8 V FPGA Family

- Densities from 58 k to 4 M system gates

- 130 MHz internal performance (four LUT levels)

- Designed for low-power operation

- PCI pliant 3.3 V, 32/64-bit, 33/ 66-MHz Highly Flexible Select I/O+™ Technology

- Supports 20 high-performance interface standards

- Up to 804 singled-ended I/Os or 344 differential I/O pairs for an aggregate bandwidth of > 100 Gb/s Differential Signalling Support

- LVDS (622 Mb/s), BLVDS (Bus LVDS), LVPECL

- Differential I/O signals can be input, output, or I/O

- patible with standard differential devices

- LVPECL and LVDS clock inputs for 300+ MHz clocks Proprietary High-Performance Select Link™ Technology

- Double Data Rate (DDR) to Virtex-E link

- Web-based HDL generation methodology Sophisticated Select RAM+™ Memory Hierarchy

- 1 Mb of internal configurable distributed RAM

- Up to 832 Kb of synchronous internal block RAM

- True Dual-Port Block RAM capability

- Memory bandwidth up to 1.66 Tb/s (equivalent...