Datasheet Summary

( DataSheet : .. )

CLA70000 Series

High Density CMOS Gate Arrays

DS2462

ISSUE 3.1

March 1992

Recent advances in CMOS processing technology and improvements in design architecture have led to the development of a new generation of array-based ASIC products with vastly improved gate integration densities. This family of CLA70000 1 micron CMOS arrays brings considerable advantages to the design of next generation systems bining high performance and high plexity.

Overview

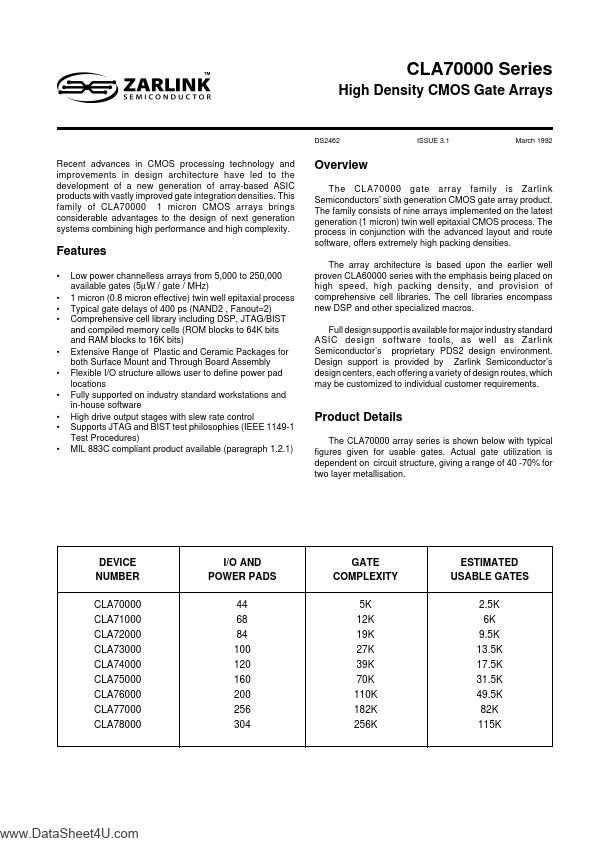

The CLA70000 gate array family is Zarlink Semiconductors' sixth generation CMOS gate array product. The family consists of nine arrays implemented on the latest generation (1 micron) twin well...